# **CM-xAM Embedded PC Module**

**Reference Guide**

August 15, 2010

© 2010 CompuLab Ltd.

All Rights Reserved. No part of this document may be photocopied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means whether, electronic, mechanical, or otherwise without the prior written permission of CompuLab Ltd.

No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law, no liability (including liability to any person by reason of negligence) will be accepted by CompuLab Ltd., its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document.

CompuLab Ltd. reserves the right to change details in this publication without notice.

Product and company names herein may be the trademarks of their respective owners.

CompuLab Ltd. P.O.B. 66 Nesher 36770 ISRAEL Tel: +972 (4) 8290100 Fax: +972 (4) 8325251 http://www.compulab.co.il/

# **Revision Information**

| Date         | Description                |  |

|--------------|----------------------------|--|

| May 10, 2010 | Intermediate Draft Release |  |

| Aug 15, 2010 | Initial release            |  |

Please check for a newer revision of this manual in CompuLab's web site -

http://www.compulab.co.il/. Compare the revision notes of the updated manual from the web site with those of the printed or electronic form version you have.

## **Table of Contents**

| 1 | IN   | NTRODUCTION                         | 9  |

|---|------|-------------------------------------|----|

|   | 1.1  | About This Document                 | 9  |

|   | 1.2  | CM-xAM Part Number Legend           | 9  |

| _ |      |                                     |    |

| 2 | 0    | VERVIEW                             |    |

|   | 2.1  | Block Diagram                       |    |

|   | 2.2  | CM-xAM Features                     |    |

|   | 2.3  | General Description                 |    |

|   | 2.4  | CPU                                 |    |

|   | 2.5  | Chipset                             |    |

|   | 2.6  | Flash Disk                          |    |

|   | 2.7  | SDRAM                               |    |

|   | 2.8  | BIOS Flash                          | 14 |

| 3 | Pl   | ERIPHERALS AND FUNCTIONS            | 15 |

|   | 3.1  | Components Locations                | 15 |

|   | 3.2  | Signal type definition              |    |

|   | 3.3  | Display Controller                  |    |

|   | 3.   | 3.1 LVDS                            |    |

|   | 3.   | 3.2 Intel Serial DVO (SDVO) Display |    |

|   | 3.4  | SATA interface                      |    |

|   | 3.5  | IDE Interface                       | 20 |

|   | 3.6  | PCI Express Interface               | 21 |

|   | 3.7  | PCI Interface                       | 22 |

|   | 3.8  | LPC Interface                       | 25 |

|   | 3.9  | Serial IRQ                          | 25 |

|   | 3.10 | Intel High Definition Audio Link    | 26 |

|   | 3.11 | USB Interface                       | 26 |

|   | 3.12 | LAN Interface                       | 27 |

|   | 3.   | 12.1 LAN1 Port                      | 28 |

|   | 3.   | 12.2 LAN2 Port                      | 28 |

|   | 3.13 | GPIO Signals                        | 29 |

|   | 3.   | 13.1 Chipset GPIO Signals           | 29 |

|   | 3.14 | I <sup>2</sup> C Interface          | 29 |

|   | 3.15 | SMBus Interface                     | 30 |

|   | 3.16 | System Signals                      | 30 |

|   | 3.17 | Power Pins                          | 31 |

|   | 3.18 | Module Type Signals                 | 31 |

| 4 | Ы    | INOUT INFORMATION                   |    |

| ſ | 4.1  | CM-xAM Connector Pinout             |    |

|   | 4.1  |                                     | 32 |

| 5 | EI                 | LECTRICAL SPECIFICATION                |  |

|---|--------------------|----------------------------------------|--|

|   | 5.1                | Power Consumption                      |  |

|   |                    | 1.1 Windows XP Idle State              |  |

|   | 5.1                | 1.2 Windows XP Running Quake III Arena |  |

| 6 | Μ                  | ECHANICAL SPECIFICATIONS               |  |

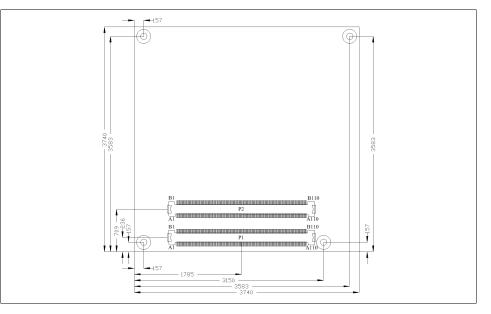

|   | 6.1                | Connector Layout                       |  |

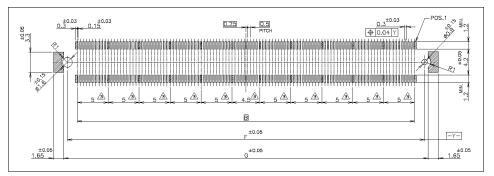

|   | 6.2 Connector Type |                                        |  |

# **List of Figures**

| Figure 1 | CM-xAM Block Diagram                        | 10 |

|----------|---------------------------------------------|----|

| Figure 2 | A mezzanine modular system example          | 12 |

| Figure 3 | CM-xAM Top Components                       | 15 |

| Figure 4 | CM-xAM Bottom Components (as seen from top) | 15 |

| Figure 5 | Connector Layout                            |    |

| Figure 6 | Connector Footprint Drawing                 |    |

# List of Tables

| Table 1  | CM-xAM configuration options                            | 9  |

|----------|---------------------------------------------------------|----|

| Table 2  | CM-xAM features                                         | 11 |

| Table 3  | CM-xAM BIOS features                                    | 11 |

| Table 4  | Electrical, Mechanical and Environmental Specifications | 11 |

| Table 5  | Signal Type Definition                                  | 16 |

| Table 6  | LVDS Interface                                          | 17 |

| Table 7  | SDVO Interface                                          | 18 |

| Table 8  | Supported PATA Standards and Modes                      | 19 |

| Table 9  | SATA Interface                                          | 19 |

| Table 10 | IDE interface signals                                   | 20 |

| Table 11 | PCIE Ports Availability and Bandwidth                   | 22 |

| Table 12 | PCI Express Interface Signals                           | 22 |

| Table 13 | PCI interface signals                                   | 23 |

| Table 14 | LPC interface signals                                   | 25 |

| Table 15 | Serial IRQ                                              | 25 |

| Table 16 | Intel HD Link Interface                                 | 26 |

| Table 17 | USB Interface                                           | 27 |

| Table 18 | LAN1 Interface                                          | 28 |

| Table 19 | LAN2 Interface                                          | 28 |

| Table 20 | SCH GPIO Signals                                        | 29 |

| Table 21 | I <sup>2</sup> C Bus Signals                            | 30 |

| Table 22 | SMBus signals                                           | 30 |

| Table 23 | System signals                                          | 30 |

| Table 24 | Power signals                                           | 31 |

| Table 25 | Module Type Signals                                     | 31 |

| Table 26 | CM-xAM COM Express Connector Rows A and B Pinout        | 32 |

| Table 27 | CM-xAM COM Express Connector Rows C and D Pinout        | 34 |

| Table 28 | Interface Connector Type                                |    |

# 1 INTRODUCTION

### 1.1 About This Document

This document is part of a set of reference documents providing information necessary to operate and program CompuLab's CM-xAM Embedded PC Module and found in the Developer section at the CompuLab Web site http://www.compulab.co.il.

## 1.2 CM-xAM Part Number Legend

CM-xAM part number format is presented below:

CM-xAM-Dx-Cx-Nx-Ex-Px-S-Yx-H-Tx-X

This part number format represents the CM-xAM configuration options available, listed in the table below:

### Table 1 CM-xAM configuration options

| Feature             | Options                          | Part Number Code |

|---------------------|----------------------------------|------------------|

| DDR SDRAM size      | 1GB DDR2                         | D1               |

| DDR SDRAM size      | 2GB DDR2                         | D2               |

| CDU type and aread  | Z530 1.6Ghz@533MHz FSB           | C16              |

| CPU type and speed  | Z510 1.1GHz@400MHz FSB           | C11              |

|                     | (none)                           | -                |

| Flash Disk size     | 1GB                              | N1               |

|                     | 4GB                              | N4               |

|                     | (none)                           | -                |

| Network interfaces  | 1 x 1000Base-T                   | E1               |

|                     | 2 x 1000Base-T                   | E2*              |

|                     | (none)                           | -                |

| DCL options         | Additional PCI Express interface | PE               |

| PCI options         | Parallel PCI interface           | PB*              |

|                     | Both of above                    | PEB              |

| Haat approadar      | (none)                           | -                |

| Heat-spreader       | Heat-spreader                    | Н3               |

|                     | Commercial                       |                  |

| Temperature range   | Extended                         | TE               |

|                     | Industrial                       | TI               |

| Software proloading | No                               | -                |

| Software preloading | Yes                              | Х                |

Note: options combination PB and E2 is illegal.

# 2 OVERVIEW

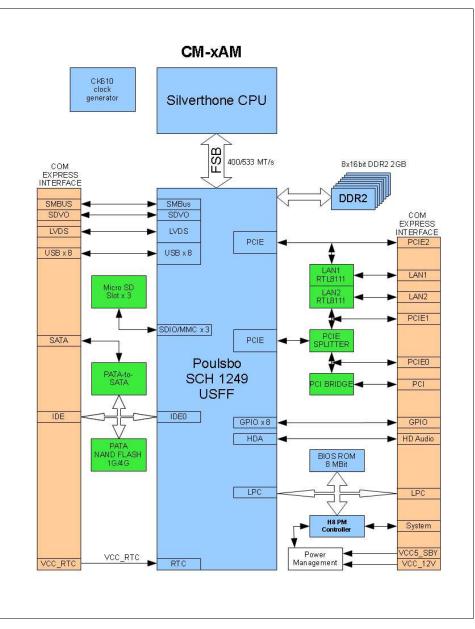

## 2.1 Block Diagram

### Figure 1 CM-xAM Block Diagram

## 2.2 CM-xAM Features

### Table 2 CM-xAM features

| Feature                                                                                                                                                                                                                                                                                     | Description                                                                                                                                                                           |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| СРИ                                                                                                                                                                                                                                                                                         | Intel Atom Processor.<br>Z530 1.6Ghz@533MHz FSB<br>or<br>Z510 1.1GHz@400MHz FSB.<br>512KB L2 (dynamic sizing), 32KB IC, 24KB DC L1.<br>Intel Deep Power Down (C6) technology support. |  |

| Chipset                                                                                                                                                                                                                                                                                     | Intel® SCH US15W Poulsbo Chipset                                                                                                                                                      |  |

| DRAM                                                                                                                                                                                                                                                                                        | 1024/2048 MB onboard 400/533 MHz, 64-bit DDR2 SDRAM                                                                                                                                   |  |

| Graphics                                                                                                                                                                                                                                                                                    | Intel® SCH integrated video controller                                                                                                                                                |  |

| Display support                                                                                                                                                                                                                                                                             | LVDS panels;<br>TV-out, VGA, DVI, LVDS by means of external SDVO                                                                                                                      |  |

| Display interfaces                                                                                                                                                                                                                                                                          | <ul> <li>LVDS with 3-pair (and clock) modes support</li> <li>SDVO</li> </ul>                                                                                                          |  |

| Network interfaces                                                                                                                                                                                                                                                                          | 1 or 2 x 1000Base-T, activity LED's                                                                                                                                                   |  |

| USB                                                                                                                                                                                                                                                                                         | <ul> <li>8 external ports</li> <li>UHCI controllers</li> <li>EHCI High-speed USB 2.0 host controller.</li> <li>USB Client Controller</li> </ul>                                       |  |

| • PCI Express (up to 3 lanes + clocks), up to 5 Gb/s concurrent bandwidth Gb/s in each direction)         • PCI: 32-bit, 33MHz, Rev 2.3, 3.3V levels, 5V tolerance, arbiter, clock         • LPC: including external boot ROM support         • Intel High Definition Audio         • SMBus |                                                                                                                                                                                       |  |

| Flash disk 1GB or 4GB, NANDrive based                                                                                                                                                                                                                                                       |                                                                                                                                                                                       |  |

| BIOS Flash                                                                                                                                                                                                                                                                                  | 1MB, on-board reprogrammable                                                                                                                                                          |  |

| External Storage • Parallel ATA with PIO, ATA-5 and Ultra DMA modes support<br>• Serial ATA port                                                                                                                                                                                            |                                                                                                                                                                                       |  |

| General purpose I/O                                                                                                                                                                                                                                                                         | 20 lines (some shared with other functions), 3.3V levels, 5V tolerant (some)                                                                                                          |  |

| Watchdog                                                                                                                                                                                                                                                                                    | Generates SMI and/or reset upon timeout                                                                                                                                               |  |

| Heat-spreader Optional heat-spreader available                                                                                                                                                                                                                                              |                                                                                                                                                                                       |  |

| Connector interface COM Express                                                                                                                                                                                                                                                             |                                                                                                                                                                                       |  |

#### Table 3 CM-xAM BIOS features

| Feature                                                                                                 | Description                                                                                |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Bootable devices Supported boot devices are HDD, USB, CD-ROM, SD-card, PX                               |                                                                                            |

| Power-on self test                                                                                      | During POST, hardware, including the CPU, RAM, and peripherals, is initialized and tested. |

| Utilities Ethrlink System Maintenance Utility for updating BIOS ROM a NAND flash through Ethernet link. |                                                                                            |

| Password protection When enabled, a password is required for POST to enter BIOS see                     |                                                                                            |

### Table 4 Electrical, Mechanical and Environmental Specifications

| Supply Voltage         | 12.0 VDC main power and 5.0 VDC standby power              |

|------------------------|------------------------------------------------------------|

| Power consumption      | 5W typical, 7.6W peak (depending on CPU type and speed)    |

| Dimensions             | 95mm x 95mm x 7.8 mm                                       |

| Weight                 | 57g max (depending on configuration) without heat spreader |

| MTBF                   | > 100,000 hours                                            |

| Operation temp. (case) | 0 to 70 °C (Commercial)                                    |

| Storage temperature    | -40 to 85 °C                                               |

| Relative humidity      | 5% to 95% (storage)<br>10% to 90% (operation)              |

| Shock                        | 50G / 20 ms    |

|------------------------------|----------------|

| Vibration                    | 20G / 0-600 Hz |

| Connector insertion/ removal | 20 cycles      |

## 2.3 General Description

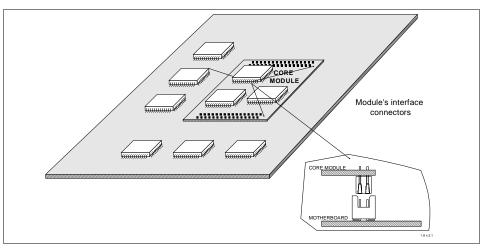

The CM-xAM module is a small COM Express-compatible single board computer. Its functional content is equivalent to that of a full-featured desktop PC. CM-xAM is intended to serve as a controller and/or user interface in embedded and mobile applications. CM-xAM is designed to plug into target application boards as a mezzanine piggyback module. It thereby replaces the components that would have been put on the application board in order to implement the required functionality. Using CM-xAM 's "off-the-shelf" solution saves months of design and debugging.

CM-xAM comes in a COM Express Compact form factor.

#### Figure 2 A mezzanine modular system example

### 2.4 CPU

The CM-xAM utilizes an Intel® Atom Z5xx series CPU.

The Intel® Atom Z5xx series processor is built with 45-nanometer process technology — the first generation of a low-power IA-32 micro-architecture specially designed for the new class of Mobile Internet Devices (MID).

The following list provides some of the key features of this processor:

- New single-core processor for mobile devices with enhanced performance

- On-die, primary 32-kB instructions cache and 24-kB write-back data cache

- 100-MHz and 133-MHz Source-Synchronous front side bus (FSB)

- Supports Hyper-Threading Technology 2-threads

- On-die 512-kB, 8-way L2 cache

- Support for IA 32-bit and Intel® 64 architecture

- Intel® Virtualization Technology (Intel® VT)

- Intel® Streaming SIMD Extensions 2 and 3 (Intel® SSE2 and Intel® SSE3) and Supplemental Streaming SIMD Extensions 3 (SSSE3) support

- Supports new CMOS FSB signaling for reduced power

- Micro-FCBGA8 packaging technologies

- Thermal management support via TM1 and TM2

- FSB Lane Reversal for flexible routing

- Supports C0/C1(e)/C2(e)/C4(e)

- New C6 Deep Power Down Technology

- L2 Dynamic Cache Sizing

- New Split-VTT support for lowest processor power state

- Advanced power management features including Enhanced Intel SpeedStep® Technology

- Executes Disable Bit support for enhanced security

## 2.5 Chipset

The CM-xAM uses an Intel® System Controller Hub (Intel® SCH) US15W Poulsbo chipset. The Intel® SCH chipset of the Atom low-power platform combines the functionality normally found in separate GMCH (integrated graphics, processor interface, memory controller) and ICH (on-board and end-user I/O expansion) components into a single component consuming less than 2.3 W of thermal design power.

## 2.6 Flash Disk

One of the key advantages of CM-xAM architecture is its high-performance, fully integrated, embedded flash solid state drives (when option Nx is selected) - SST85LD1001K (N1) or SST85LD1004M (N4) NANDrive<sup>™</sup> integrated circuits (IC).

It combines an integrated ATA Controller and either 1Gbyte or 4Gbytes of NAND Flash in a multi-chip package. This solution is ideal for solid-state mass storage applications offering new and expanded functionality while enabling cost-effective designs.

The SST NANDrive is a single solid-state drive device, designed for embedded ATA/IDE protocol systems supporting a standard ATA/IDE protocol with up to PIO Mode-6, Multi-word DMA Mode-4 and Ultra DMA Mode-4 interfaces. The built-in micro-controller and file management firmware communicates with ATA standard interfaces thereby eliminating the need for additional or proprietary software such as Flash File System (FFS) and Memory Technology Driver (MTD) software.

The Flash Disk behaves exactly like a regular hard disk drive; however, it doesn't have any moving parts and is built into the CM-xAM module.

The NAND Flash provides a storage solution for embedded applications requiring nonvolatile on-board storage. The NAND Flash is a block device - optimized for block read and write operations rather than for random access. The NAND Flash is interfaced through a standard ATA-based IDE port and is configured as a primary master device by default.

Key Features:

- Industry Standard ATA/IDE Bus Interface

- Host Interface: 16-bit access

- Supports up to PIO Mode-6

- Supports up to Multi-word DMA Mode-4

- Supports up to Ultra DMA Mode-4

- Advanced power management

- Zero wake-up latency

- Expanded Data Protection

- Data security through user-selectable protection

- User-Programmable 10-byte ID

- Prevents data loss due to unexpected power-down or brownout

- 10 Million write cycles with advanced NAND management technology

- 3 year data retention

- Robust Built-in ECC

#### Performance

| Read  | Up to 30Mb/s |

|-------|--------------|

| Write | Up to 8Mb/s  |

### 2.7 SDRAM

CM-xAM can be assembled with up to 2048 Mbytes of DDR2 Synchronous DRAM (DDR2 SDRAM). All SDRAM components are soldered on-board (rather than connected with SODIMM), in order to provide better mechanical reliability, required by most embedded applications. The user selects DDR SDRAM size upon ordering.

## 2.8 BIOS Flash

BIOS and other initialization code are contained in the LPC ROM component, which is implemented by a 1024 KB flash memory. BIOS ROM is used only for keeping BIOS and BIOS-related settings, all other code and data should be stored in the Nand flash or hard disks. Bios ROM is re-programmable on-board and supports field updates of BIOS code.

# **3 PERIPHERALS AND FUNCTIONS**

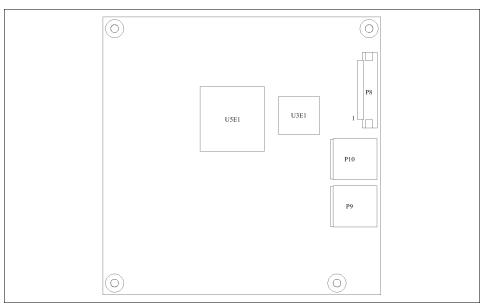

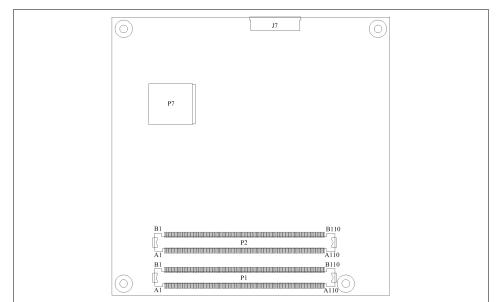

## 3.1 Components Locations

### Figure 3 CM-xAM Top Components

### Figure 4 CM-xAM Bottom Components (as seen from top)

## 3.2 Signal type definition

#### Table 5 Signal Type Definition

| Туре | Name                  | Description                                                                                           |

|------|-----------------------|-------------------------------------------------------------------------------------------------------|

| Ι    | Digital Input         | CMOS Input pin                                                                                        |

| 0    | Digital Output        | CMOS Output pin                                                                                       |

| I/O  | Digital Input/Output  | CMOS Multiplexed input and output pin to and from CM-xAM                                              |

| OD   | Open Drain            | CMOS Open drain output pin, possibly with integrated pull-up                                          |

| I/OD | Input/Open Drain      | CMOS Multiplexed input and open drain output pin to and from CM-xAM, possibly with integrated pull-up |

| IDIF | Differential (Input)  |                                                                                                       |

| ODIF | Differential (Output) |                                                                                                       |

| DIFF | Differential (Bidir)  |                                                                                                       |

## 3.3 Display Controller

The CM-xAM graphics system is built on the Intel® SCH integrated graphics controller, based on Intel® GMA500 architecture. The highly compact Integrated Graphics Device (IGD) contains advanced shader architecture (model 3.0+) that performs pixel shading and vertex shading within a single hardware accelerator. The processing of pixels is deferred until they are determined to be visible, which minimizes access to memory and improves render performance.

Key Features:

- Flexible Programmable Architecture

- Shader-based technology

- 3D Graphics

- 2D and advanced 2D Graphics

- Video Encode / Decode support

- Image processing

- Deferred Pixel Shading

- Screen Tiling

- On-chip Stencil, Z and Frame buffers

- High Performance

- Low Power

- Industry standard tool support

- Comprehensive OS/API support

#### 3-D Core Key Features:

- Two pipe scaleable unified shader implementation

- 3-D Peak Performance

- Fill Rate: 2 Pixels per clock

- Vertex Rate: One Triangle 15 clocks (Transform Only)

- Vertex / Triangle Ratio average = 1 vtx/tri, peak 0.5 vtx/tri

- Texture max size =  $2048 \times 2048$

- Programmable 4x multi-sampling anti-aliasing (MSAA)

- Rotated grid

- ISP performance related to AA mode, TSP performance unaffected by AA mode

- Optimized memory efficiency using multi-level cache architecture

Video Decode Overview

The video decode accelerator improves video performance-power ratio by providing hardware-based acceleration at the macroblock level (variable length decode stage entry point). The Intel SCH supports full hardware acceleration of the following video decode standards:

| CODEC | PROFILE                 | LEVEL                    |

|-------|-------------------------|--------------------------|

| H.264 | Baseline profile        | L3                       |

| H.264 | Main profile            | L4.1 (1080i @ 30fps)     |

| H.264 | High profile            | L4.1 (1080i @ 30fps)     |

| MPEG2 | Main profile            | High                     |

| MPEG4 | Simple profile          | L3                       |

| MPEG4 | Advanced simple profile | L5                       |

| VC1   | Simple profile          | Medium                   |

| VC1   | Main profile            | High                     |

| VC1   | Advanced profile        | L3 up to (1080i @ 30fps) |

| WMV9  | Simple profile          | Medium                   |

| WMV9  | Main profile            | High                     |

The video decode function is performed in four processing modules:

- Entropy coding processing

- Motion compensation

- Deblocking

- Final pixel formatting

The IGD includes LVDS and Serial DVO display ports permitting simultaneous independent operation of two displays – LVDS and SDVO. Carrier board may also implement an LVDS to parallel 24-bit RGB converter allowing the connection of different parallel LCD's.

#### 3.3.1 LVDS

The System Controller Hub (Poulsbo SCH) supports a Low-Voltage Differential Signaling interface allowing the IGD to communicate directly with a flat-panel display. The LVDS interface supports pixel color depth of 18 or 24 bits and max pixel clock of 112 MHz

#### Table 6LVDS Interface

| Signal Name | COM<br>Express<br>Pin | Туре | Description              |

|-------------|-----------------------|------|--------------------------|

| LVDS_A0+    | A71                   | ODIF | LVDS Differential Pair 0 |

| LVDS_A0-    | A72                   | ODIF | LVDS Differential Pail 0 |

| LVDS_A1+    | A73                   | ODIF | LVDS Differential Pair 1 |

| LVDS_A1-    | A74                   | ODIF |                          |

| LVDS_A2+    | A75                   | ODIF | LVDS Differential Pair 2 |

| LVDS_A2-    | A76                   | ODIF |                          |

| Signal Name    | COM<br>Express<br>Pin | Туре | Description                                                         |

|----------------|-----------------------|------|---------------------------------------------------------------------|

| LVDS_A3+       | A78                   | ODIF | LVDS Differential Pair 3                                            |

| LVDS_A3-       | A79                   | ODIF | LVDS Differential Fail 5                                            |

| LVDS_A_CK+     | A81                   | ODIF | LVDS Differential Clock                                             |

| LVDS_A_CK-     | A82                   | ODIF | LVDS Differential Clock                                             |

| LVDS_I2C_CK    | A83                   | I/O  | LVDS DDC Clock                                                      |

| LVDS_I2C_DAT   | A84                   | I/O  | LVDS DDC Data                                                       |

| LVDS_VDD_EN    | A77                   | 0    | Power sequencing control for panel driver electronics               |

| LVDS_BKLT_EN   | B79                   | 0    | Panel backlight enable                                              |

| LVDS_BKLT_CTRL | B83                   | 0    | LCD Backlight Control: This signal allows control of LCD brightness |

### 3.3.2 Intel Serial DVO (SDVO) Display

The SCH has a digital display channel capable of driving SDVO adapters providing interfaces to a variety of external display technologies (e.g., DVI, analog CRT). Up to 160 MHz pixel clock supported.

CM-xAM outputs SDVO interface signals on the COM Express PCI Express Graphics pins.

#### Table 7SDVO Interface

| Signal Name    | COM<br>Express<br>Pin | Туре | Description                                   |

|----------------|-----------------------|------|-----------------------------------------------|

| SDVO_BCLK+     | D61                   | ODIF | Serial Digital Video Channel B Clock          |

| SDVO_BCLK-     | D62                   | ODIF | Senai Digitai Video Channel B Clock           |

| SDVO_BLUE+     | D58                   | ODIF | Social Digital Vidao Channel P. Phys          |

| SDVO_BLUE-     | D59                   | ODIF | Serial Digital Video Channel B Blue           |

| SDVO_RED+      | D52                   | ODIF | Serial Digital Video Channel B Red            |

| SDVO_RED-      | D53                   | ODIF | Senai Digitai Video Chainei B Ked             |

| SDVO_GREEN+    | D55                   | ODIF | Serial Digital Video Channel B Green          |

| SDVO_GREEN-    | D56                   | ODIF | Senai Digitai video Chainer B Green           |

| SDVO_INT+      | C55                   | IDIF | Serial Digital Video Input Interrupt          |

| SDVO_INT-      | C56                   | IDIF | Senai Digitai video input interrupt           |

| SDVO_FLDSTALL+ | C58                   | IDIF | Serial Digital Video Field Stall              |

| SDVO_FLDSTALL- | C59                   | IDIF | Senai Digitai video Field Stali               |

| SDVO_TVCLKIN+  | C52                   | IDIF | Serial Digital Video TV-OUT Sync Clock pair   |

| SDVO_TVCLKIN-  | C53                   | IDIF | Serial Digital video 1 v-001 Sylle Clock pall |

| SDVO_CTRL_CLK  | D73                   | I/O  | SDVO Control Clock (similar to I2C)           |

| SDVO_CTRL_DAT  | C73                   | I/O  | SDVO Control Data (similar to I2C)            |

Notes:

- SDVO signals are compatible with PCI Express 1.0a Signaling Environment AC Specifications and are AC coupled. The buffers are not 3.3-V tolerant. Differential voltage specification = (|D+ D-|) \* 2 = 1.2V max. Single-ended maximum =1.5V. Single-ended minimum = 0V.

- 100 nF decoupling capacitor must be used on all differential SDVO signals (see SB-xAM reference schematic)

## 3.4 SATA interface

This interface is available only in modules with the "S" option.

The CM-xAM Serial ATA (SATA) interface is formed from the PATA interface using a PATA to SATA bridge. The CM-xAM ATA (PATA) interface is provided directly by an Intel® SCH PATA controller. PATA interface supports only the primary channel, with one master and one slave device.

Three types of data transfers are supported:

- Programmed I/O (PIO): A protocol used to transfer data between the processor as the ATA device. PIO allows transfer rates of up to 16MB/s.

- Multi-word DMA: DMA protocol that resembles the DMA on the ISA bus. Allows transfer rates of up to 16MB/s.

- Ultra-DMA: Source synchronous DMA protocol allowing transfer rates of up to 100MB/s.

#### Table 8 Supported PATA Standards and Modes

| PATA Standard                         | Transfer Modes Supported                         | Transfer Rate<br>(MB/s)    |

|---------------------------------------|--------------------------------------------------|----------------------------|

| A.T.A. 1                              | PIO Modes 0, 1, 2                                | 3.3, 5.2, 8.3              |

| ATA-1<br>(ATA, IDE)                   | Single-word DMA Modes 0, 1, 2                    | 2.1, 4.2, 8.3              |

| (AIA, IDL)                            | Multi-word DMA Mode 0                            | 4.2                        |

| ATA-2, ATA-3<br>(EIDE, Fast ATA)      | PIO Modes 3, 4                                   | 11.1, 16.6                 |

|                                       | Multi-word DMA Modes 1, 2                        | 13.3, 16.6                 |

| ATA/ATAPI-4<br>(Ultra DMA, Ultra ATA) | Ultra DMA Modes 0, 1, 2<br>(a.k.a. Ultra DMA/33) | 16.7, 25.0, 33.3           |

| ATA/ATAPI-5<br>(Ultra DMA, Ultra ATA) | Ultra DMA Modes 3, 4<br>(a.k.a. Ultra DMA/66)    | 44.4, 66.7                 |

| ATA/ATAPI-6<br>(Ultra DMA, Ultra ATA) | Ultra-DMA Mode 5<br>(a.k.a. Ultra DMA/100)       | 100 (reads)<br>89 (writes) |

PATA to SATA bridge key features are:

- SATA-II with 1.5 Gb/s operation support

- SATA 2.6 Compliant

- ATA/ATAPI 48-bit address feature set

- ATA/ATAPI 7 feature set

- Tagged command queuing (maximum 32 entries)

- SATA power save modes

#### Table 9SATA Interface

| Signal Name | COM<br>Express<br>Pin | Туре | Description            |

|-------------|-----------------------|------|------------------------|

| SATA_TX+    | A16                   | ODIF | SATA transmit pair     |

| SATA_TX-    | A17                   | ODIF | SATA transmit pan      |

| SATA_RX+    | A19                   | IDIF | SATA receive pair      |

| SATA_RX-    | A20                   | IDIF | SATA leceive pair      |

| ATA_ACT#    | A28                   | 0    | SATA/PATA activity led |

## 3.5 IDE Interface

IDE interface is unavailable in modules with both "Nx" (Nand) and "S" (Sata) options chosen. When only one of the "Nx" or "S" options chosen, only a slave device may be connected on the external IDE interface. When no "S" or "Nx" options chosen, both slave and master are available.

IDE interface is also unavailable in modules with "E2" option chosen, because IDE bus shares connector pins with LAN2 interface.

### Table 10 IDE interface signals

| CM-xAM Signal<br>Name | COM<br>Express<br>Pin | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                |  |

|-----------------------|-----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IDE_CS1#              | D16                   | 0    | IDE Device Chip Selects for 100 Range: For ATA command<br>register block. This output signal to be connected to the CS1# signal<br>on the IDE connector.                                                                                                                                                                                                                                                   |  |

| IDE_CS3#              | D17                   | 0    | IDE Device Chip Select for 300 Range: For ATA control register block. This output signal is to be connected to the CS3# signal on the IDE connector.                                                                                                                                                                                                                                                       |  |

| IDE_A0                | D13                   |      | IDE Device Address: These output signals are connected to the                                                                                                                                                                                                                                                                                                                                              |  |

| IDE_A1                | D14                   | 0    | corresponding signals on the IDE connector. They indicate which<br>byte in either the ATA command block or control block is being                                                                                                                                                                                                                                                                          |  |

| IDE_A2                | D15                   |      | addressed.                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| IDE_D0                | D7                    |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D1                | C10                   |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D2                | C8                    |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D3                | C4                    |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D4                | D6                    |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D5                | D2                    |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D6                | C3                    |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D7                | C2                    | I/O  | IDE Device Data: These signals directly drive the corresponding                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D8                | C6                    | 10   | signals on the IDE connector.                                                                                                                                                                                                                                                                                                                                                                              |  |

| IDE_D9                | C7                    | -    |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D10               | D3                    |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D11               | D4                    |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D12               | D5                    |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D13               | C9                    |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D14               | C12                   |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_D15               | C5                    |      |                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| IDE_DREQ              | D8                    | I    | IDE Device DMA Request: This input signal is directly driven from<br>the DRQ signal on the IDE connector. It is asserted by the IDE<br>device to request a data transfer, is used in conjunction with the PCI<br>bus master IDE function and is not associated with any AT<br>compatible DMA channel. There is a weak internal pull-down<br>resistor on this signal.                                       |  |

| IDE_DACK#             | D10                   | 0    | IDE Device DMA Acknowledge: This signal directly drives the DAK# signal on the IDE connector. It is asserted by the IDE controller to indicate to IDE DMA slave devices that a given data transfer cycle (assertion of IDE-RD# or IDE-WR#) is a DMA data transfer cycle. This signal is used in conjunction with the PCI bus master IDE function and is not associated with any AT-compatible DMA channel. |  |

| CM-xAM Signal<br>Name | COM<br>Express<br>Pin | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | 614                   | 0    | <ul> <li>Disk I/O Read (PIO and Non-Ultra DMA): This is the<br/>command to the IDE device that it may drive data onto the LB-<br/>D[15:0] lines. Data is latched by the IDE controller on the de-<br/>assertion edge of IDE-RD#. The IDE device is selected either<br/>by the ATA register file chip selects (IDE-CS0# and IDE-<br/>CS1#) and the LB-A[2:0] lines, or the IDE DMA acknowledge<br/>(IDE-DACK#).</li> </ul> |

| IDE_RD#               | C14                   | 0    | <ul> <li>Disk Write Strobe (Ultra DMA Writes to Disk): This is the data<br/>write strobe for writes to disk. When writing to disk, IDE<br/>controller drives valid data on rising and falling edges of IDE-<br/>RD#.</li> </ul>                                                                                                                                                                                           |

|                       |                       |      | <ul> <li>Disk DMA Ready (Ultra DMA Reads from Disk): This is the<br/>DMA ready for reads from disk. When reading from disk, IDE<br/>controller de-asserts IDE-RD# to pause burst data transfers.</li> </ul>                                                                                                                                                                                                               |

| IDE_WR#               | D9                    | 0    | <ul> <li>Disk I/O Write (PIO and Non-Ultra DMA): This is the<br/>command to the IDE device that it may latch data from the LB-<br/>D[15:0] lines. Data is latched by the IDE device on the de-<br/>assertion edge of IDE-WR#. The IDE device is selected either<br/>by the ATA register file chip selects (IDE-CS0# and IDE-<br/>CS1#) and the LB-A[2:0] lines, or the IDE DMA acknowledge<br/>(IDE-DACK#).</li> </ul>    |

|                       |                       |      | • Disk Stop (Ultra DMA): asserted by the host to terminate a burst.                                                                                                                                                                                                                                                                                                                                                       |

| IDE_RDY#              | C13                   | I    | <ul> <li>I/O Channel Ready (PIO): This signal will keep the strobe<br/>active (IDE-RD# on reads, IDE-WR# on writes) longer than<br/>the minimum width. It adds wait states to PIO transfers. Disk<br/>Read Strobe (Ultra DMA Reads from Disk): When reading<br/>from disk, ide controller latches data on rising and falling edges<br/>of this signal from the disk.</li> </ul>                                           |

|                       |                       |      | <ul> <li>Disk DMA Ready (Ultra DMA Writes to Disk): When writing<br/>to disk, this is de-asserted by the disk to pause burst data<br/>transfers.</li> </ul>                                                                                                                                                                                                                                                               |

| IDE_IRQ               | D12                   | Ι    | <b>IDE Interrupt Request:</b> This interrupt input is connected to the IDE drives.                                                                                                                                                                                                                                                                                                                                        |

| IDE_CBLID#            | D77                   | I    | Input from off-module hardware indicating the type of IDE cable being used. High indicates a 40-pin cable used for legacy IDE modes. Low indicates that an 80-pin cable with interleaved grounds is used. Such a cable is required for Ultra-DMA 66,100 modes.                                                                                                                                                            |

## 3.6 PCI Express Interface

The CM-xAM contains up to three x1 PCI Express expansion interfaces supporting the PCI Express Base Specification Revision 1.0a configured as two x1 lanes. Each root port supports up to 2.5 GB/s bandwidth in each direction.

It is a high-bandwidth, low pin-count serial interface ideal for I/O expansion. An external graphics device can be used via one of the x1 PCI Express lanes/ports.

PCI Express ports availability depends on the CM-xAM module configuration. The options, which affect the PCIE availability, are Ex and Px. The following table defines PCIE ports availability as function of various options chosen.

#### Table 11 PCIE Ports Availability and Bandwidth

| Options | No P                                        | PE                                              | PB                              | PEB                                            |

|---------|---------------------------------------------|-------------------------------------------------|---------------------------------|------------------------------------------------|

| No E    | PCIE1 @ full BW<br>PCIE2 @ full BW          | PCIE0 @ ½ BW<br>PCIE1 @ ½ BW<br>PCIE2 @ full BW | PCIE2 @ full BW                 | PCIE1 @ ½ BW<br>PCIE2 @ full BW                |

| E1      | PCIE1 @ full BW<br>LAN1 @ full BW           | PCIE0 @ ½ BW<br>PCIE1 @ ½ BW<br>LAN1 @ full BW  | No PCIE ports<br>LAN1 @ full BW | PCIE1 @ ½ BW<br>LAN1 @ full BW                 |

| E2      | No PCIE ports<br>LAN1 and LAN2 @<br>full BW | PCIE0 @ ½ BW<br>LAN1 @ full BW<br>LAN2 @ ½ BW   | Invalid option configuration    | No PCIE ports<br>LAN1 @ full BW<br>LAN2 @ ½ BW |

Note: options "PE" and "PEB" add another PCIE lane, if possible, as compared to "No P" and "PB" options. This is accomplished by splitting the existing port's bandwidth, meaning that the total bandwidth of additional port and the splitted port will be 2.5 GB/s in each direction at full load.

| Signal Name  | COM<br>Express<br>Pin | Туре | Description                                                                                     |

|--------------|-----------------------|------|-------------------------------------------------------------------------------------------------|

| PCIE_TX0+    | A68                   | ODIF | DCIE0 transmit asia                                                                             |

| PCIE_TX0-    | A69                   | ODIF | PCIE0 transmit pair                                                                             |

| PCIE_RX0+    | B68                   | IDIF | PCIE0 receive pair                                                                              |

| PCIE_RX0-    | B69                   | IDIF | PCIEO receive pan                                                                               |

| PCIE_TX1+    | A64                   | ODIF | PCIE1 transmit pair                                                                             |

| PCIE_TX1-    | A65                   | ODIF |                                                                                                 |

| PCIE_RX1+    | B64                   | IDIF | PCIE1 receive pair                                                                              |

| PCIE_RX1-    | B65                   | IDIF | PCIEI receive pair                                                                              |

| PCIE_TX2+    | A61                   | ODIF | PCIE2 transmit pair                                                                             |

| PCIE_TX2-    | A62                   | ODIF |                                                                                                 |

| PCIE_RX2+    | B61                   | IDIF | PCIE2 receive pair                                                                              |

| PCIE_RX2-    | B62                   | IDIF | PCIEZ receive pair                                                                              |

| PCIE_CK_REF+ | A88                   | ODIF | PCIE differential clock reference                                                               |

| PCIE_CK_REF- | A89                   | ODIF | PCIE differential clock felerence                                                               |

| EXCD0_PERST# | A48                   | 0    | Express Card Reset, port PCIE0                                                                  |

| EXCD0_CPPE#  | A49                   | Ι    | Express Card capable card request, port PCIE0                                                   |

| EXCD1_PERST# | B47                   | 0    | Express Card Reset, port PCIE1                                                                  |

| EXCD1_CPPE#  | B48                   | Ι    | Express Card capable card request, port PCIE1                                                   |

| PCIE_WAKE#   | B66                   | Ι    | PCI Express Wake Event: This signal indicates that a PCI Express port wants to wake the system. |

#### Table 12 PCI Express Interface Signals

Notes:

- PCIE differential signals are compatible with PCI Express 1.0a Signaling Environment AC Specifications and are AC coupled. The buffers are not 3.3-V tolerant. Differential voltage specification = (|D+ - D-|) \* 2 = 1.2 Vmax. Singleended maximum =1.5 V. Single-ended minimum = 0 V.

- 100nF decoupling capacitor must be used on the receiver side (\_RX\* signals on baseboard interface connector. See SB-XAM reference schematic.

## 3.7 PCI Interface

PCI interface is available only on the modules with "PB" or "PEB" options.

CM-xAM PCI signals are driven by a PCIE-to-PCI bridge. Output drive and maximum load specifications are according to PCI bus Standard Rev-2.3.

### Table 13 PCI interface signals

|                      | СОМ        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

|----------------------|------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CM-xAM Signal        | Express    | Туре                                    | Description                                                                                                                                                                                                                                                                                                                      |     |     |                                                                                                                                                                                                                                        |

| Name                 | Pin        | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 2 coorprort                                                                                                                                                                                                                                                                                                                      |     |     |                                                                                                                                                                                                                                        |

| PCI_AD0              | C24        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD1              | D22        | 1                                       |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD2              | C25        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD3              | D23        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD4              | C26        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD5              | D24        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD6              | C27        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD7              | D25        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD8              | C28        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD9              | D27        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD10             | C29        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD11             | D28        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD12             | C30        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

|                      | D29        |                                         | Address / Data:                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD13             |            |                                         | Multiplexed address and data bus. Address phase is aligned with first clock of FRAME# assertion. Data phase                                                                                                                                                                                                                      |     |     |                                                                                                                                                                                                                                        |

| PCI_AD14<br>PCI_AD15 | C32        |                                         | is aligned with IRDY# or TRDY# assertion. Data phase                                                                                                                                                                                                                                                                             |     |     |                                                                                                                                                                                                                                        |

| _                    | D30<br>D37 | I/O                                     | transferred on rising edges of PCI_CLK when both                                                                                                                                                                                                                                                                                 |     |     |                                                                                                                                                                                                                                        |

| PCI_AD16             | -          |                                         | IRDY# and TRDY# are asserted. During bus idle (both                                                                                                                                                                                                                                                                              |     |     |                                                                                                                                                                                                                                        |

| PCI_AD17             | C39<br>D38 |                                         | FRAME# and IRDY# are deasserted), CM-xAM drives<br>AD to a valid logic level when arbiter is parking to the                                                                                                                                                                                                                      |     |     |                                                                                                                                                                                                                                        |

| PCI_AD18             | D38<br>C40 |                                         | PCI bridge on PCI bus.                                                                                                                                                                                                                                                                                                           |     |     |                                                                                                                                                                                                                                        |

| PCI_AD19             |            | -                                       |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |

| PCI_AD20             | D39        |                                         |                                                                                                                                                                                                                                                                                                                                  |     |     |                                                                                                                                                                                                                                        |