**Reference Guide**

© 2014 CompuLab Ltd.

All Rights Reserved. No part of this document may be photocopied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means whether, electronic, mechanical, or otherwise without the prior written permission of CompuLab Ltd.

No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law no liability (including liability to any person by reason of negligence) will be accepted by CompuLab Ltd., its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document.

CompuLab Ltd. reserves the right to change details in this publication without notice.

Product and company names herein may be the trademarks of their respective owners.

CompuLab Ltd. P.O. Box 687 Yokneam Elite 20692 ISRAEL Tel: +972 (4) 8290100 http://www.compulab.co.il Fax: +972 (4) 8325251

# **Table of Contents**

| 1 | INTRO    | DDUCTION                                 | 7  |

|---|----------|------------------------------------------|----|

|   | 1.1 Abc  | out This Document                        | 7  |

|   |          | -T54 Part Number Legend                  |    |

|   |          | ated Documents                           |    |

|   |          |                                          |    |

| 2 | OVER     | VIEW                                     | 8  |

|   | 2.1 Hig  | hlights                                  | 8  |

|   | 2.2 Bloc | ck Diagram                               | 9  |

|   | 2.3 CM   | -T54 Features                            | 10 |

| 3 | CORE     | SYSTEM COMPONENTS                        | 12 |

|   | 3.1 OM   | AP5432 SoC                               | 12 |

|   |          | timedia System                           |    |

|   | 3.2.1    | 3D and 2D Acceleration                   |    |

|   | 3.2.2    | DSP subsystem                            |    |

|   | 3.2.3    | IVA-HD Subsystem                         |    |

|   | 3.3 Mer  | nory                                     |    |

|   | 3.3.1    | DRAM                                     | 14 |

|   | 3.3.2    | On-board eMMC storage                    | 14 |

| 4 | PERIF    | PHERAL INTERFACES                        | 15 |

|   | 4.1 Seri | al ATA Interface                         | 16 |

|   |          | blay Interfaces                          |    |

|   | 4.2.1    | Parallel Display Interface (DPI)         |    |

|   | 4.2.2    | Remote Frame buffer interface (RFBI)     |    |

|   | 4.2.3    | LVDS Display interface                   |    |

|   | 4.2.4    | MIPI Display Interface                   |    |

|   | 4.2.5    | HDMI port                                | 20 |

|   | 4.3 Can  | nera Interfaces                          | 21 |

|   | 4.3.1    | Parallel Camera Interface                | 21 |

|   | 4.3.2    | MIPI camera interfaces MIPI-CSI          | 22 |

|   | 4.4 Aud  | lio Subsystem                            | 23 |

|   | 4.4.1    | Analog Audio CODEC                       | 23 |

|   | 4.4.2    | Digital Audio Interfaces                 | 25 |

|   | 4.4.     | 2.1 McBSP interface                      | 25 |

|   | 4.4.     | 2.2 McASP interface                      | 25 |

|   | 4.4.     | 2.3 Digital Microphone Interface         | 26 |

|   | 4.5 Hig  | h-Definition Multimedia Interface (HDMI) | 27 |

|   | 4.6 WL   | AN and Bluetooth                         | 27 |

|   | 4.7 Ethe | ernet                                    | 29 |

|   |          | 3 interfaces                             | 20 |

|   | 4.   | 8.1 USB 3.0 On-The-Go                                | . 29 |

|---|------|------------------------------------------------------|------|

|   | 4.   | 8.2 USB 2.0 Host                                     | . 30 |

|   | 4.9  | UARTs                                                | . 31 |

|   | 4.10 | RS232                                                | . 32 |

|   | 4.11 | MMC / SD / SDIO                                      | . 33 |

|   | 4.12 | Touch-Screen                                         | . 34 |

|   | 4.13 | Keypad                                               | . 34 |

|   | 4.14 | GPIO                                                 | . 35 |

|   | 4.15 | I <sup>2</sup> C                                     | . 37 |

|   | 4.16 | SPI                                                  | . 38 |

|   | 4.17 | General Purpose Timers and PWM                       | . 38 |

|   | 4.18 | HDQ / 1-Wire                                         | . 39 |

|   | 4.19 | General Purpose ADC (GPADC)                          |      |

|   | 4.20 | General purpose clock                                |      |

|   | 4.21 | JTAG                                                 | . 40 |

|   |      |                                                      |      |

| 5 | S    | YSTEM LOGIC                                          | . 42 |

|   | 5.1  | Power Supply                                         | . 42 |

|   | 5.2  | Power Management                                     | . 42 |

|   | 5.   | 2.1 Power Resources & control signals                |      |

|   | 5.   | 2.2 CM-T54 Power states                              | . 43 |

|   | 5.   | 2.3 Power-On & Power-Off                             | . 44 |

|   |      | 5.2.3.1 ON, OFF requests and gating conditions       | . 44 |

|   |      | 5.2.3.2 ON, OFF and gating signals active by default | . 45 |

|   | 5.3  | Reset                                                | . 45 |

|   | 5.4  | Boot Sequence                                        | . 46 |

|   | 5.5  | Battery & Charger signals                            | . 46 |

|   | 5.6  | Signal Multiplexing Characteristics                  | . 47 |

|   | 5.7  | RTC                                                  | . 49 |

|   | 5.8  | LED                                                  | . 49 |

|   | G    |                                                      | =0   |

| 6 |      | ARRIER BOARD INTERFACE                               |      |

|   | 6.1  | Connector Pinout                                     |      |

|   | 6.2  | Mating Connectors                                    | . 54 |

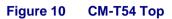

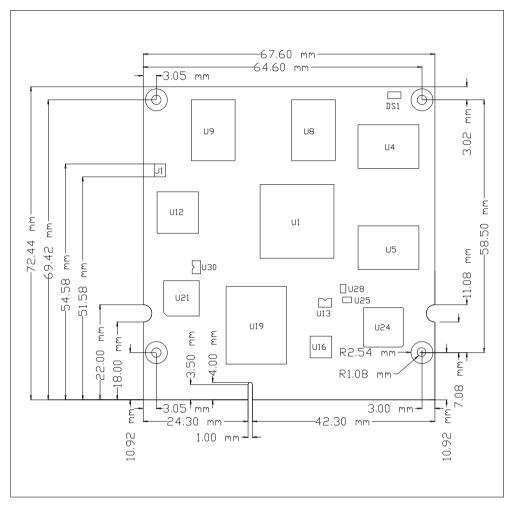

|   | 6.3  | Mechanical Drawings                                  |      |

|   | 6.4  | Standoffs/Spacers                                    | . 56 |

| 7 | Λ    | PERATIONAL CHARACTERISTICS                           | 57   |

| 1 |      |                                                      |      |

|   | 7.1  | Absolute Maximum Ratings                             |      |

|   | 7.2  | Recommended Operating Conditions                     |      |

|   | 7.3  | DC Electrical Characteristics                        |      |

|   | 7.4  | ESD Performance                                      |      |

|   | 7.5  | Operating Temperature Ranges                         | . 58 |

| 8 | Α   | PPLI | CATION NOTES                  | 59 |

|---|-----|------|-------------------------------|----|

|   | 8.1 | Carr | ier Board Design Guidelines   | 59 |

|   |     |      | ier Board Troubleshooting     |    |

|   | 8.3 | Ethe | rnet Magnetics Implementation | 60 |

|   | 8.  | 3.1  | Magnetics Selection           | 60 |

|   | 8.  | 3.2  | Magnetics Connection          | 60 |

|   | 8.4 | Heat | -plate Integration            | 60 |

| Date                   | Description                                                                                                           |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|

| Mar 2014 First release |                                                                                                                       |  |  |

| May 2014               | Fixed PMIC_PWRON pin# to 165 instead of 162 in table 44.<br>Fixed Table 22 heading to "USB 3.0 OTG interface signals" |  |  |

| June 2014              | Table 51: CM-T54 connector implementation revised to "2-sides PCB based SODIMM-204 edge connector"                    |  |  |

#### Table 1Revision Notes

Please check for a newer revision of this manual at the CompuLab web site http://www.compulab.co.il/. Compare the revision notes of the updated manual from the web site with those of the printed or electronic version you have.

# 1 INTRODUCTION

### 1.1 About This Document

This document is part of a set of reference documents providing information necessary to operate and program CompuLab CM-T54 Computer-on-Module.

### 1.2 CM-T54 Part Number Legend

Please refer to the CompuLab website 'Ordering information' section to decode the CM-T54 part number: http://compulab.co.il/products/computer-on-modules/CM-T54/#ordering.

### 1.3 Related Documents

For additional information, refer to the documents listed in Table 2.

#### Table 2 Related Documents

| Document                   | Location                           |

|----------------------------|------------------------------------|

| CM-T54 Developer Resources | http://www.compulab.com/           |

| OMAP5432 Reference Manual  | http://www.ti.com/product/omap5432 |

| OMAP5432 Datasheet         | http://www.ti.com/product/omap5432 |

|                            |                                    |

|                            |                                    |

### 2 OVERVIEW

### 2.1 Highlights

- Texas Instruments OMAP5 Dual core ARM Cortex-A15 MPCore processor capable of speeds up to 1.5 GHz

- ARM Cortex-M4 processors for low-power offload and real-time responsiveness.

- Up to 4GB Dual Channel DDR3

- Up to 32GB on-board eMMC storage

- Multi-core POWERVR<sup>TM</sup> SGX544-MPx graphics accelerators

- Dedicated TI 2D BitBlt graphics accelerator

- IVA-HD hardware accelerators enable full HD, multi-standard video encode/decode as well as stereoscopic 3D (S3D)

- HDMI 1.4, LVDS, SATAII (3Gbps), USB3.0 Host + OTG x 1, USB2.0 Host x3, UART x4, SDIO x3, ADC, Onboard WiFi 802.11b/g/n (2.4GHz), Bluetooth 3.0.

- Miniature size: 72 x 68 x 5 mm

- SB-T54 carrier board turns the CM-T54 module into SBC-T54 a single board computer

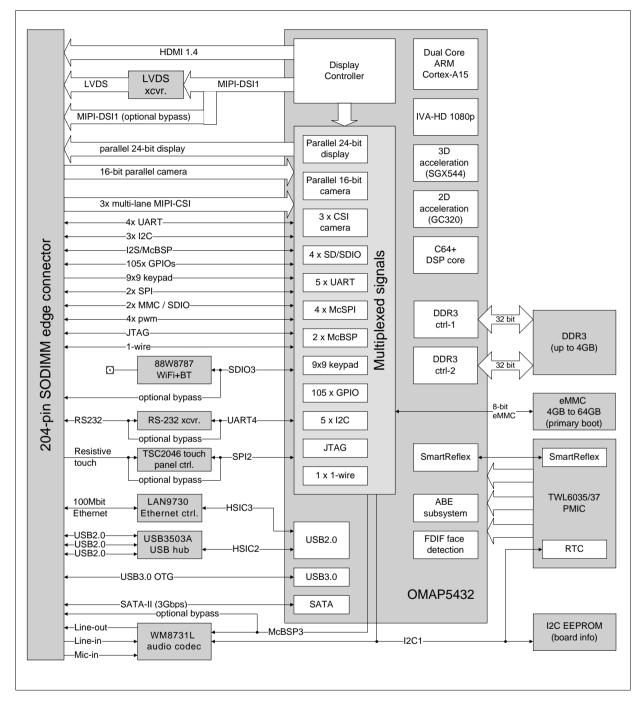

### 2.2 Block Diagram

### 2.3 CM-T54 Features

The "Option" column specifies the configuration code required to have the particular feature. "+" means that the feature is always available. Strikethrough option means that the option must not be chosen for the feature to be available.

#### Table 3 System and Graphics

| Feature                           | Specifications                                                                                                                                                                                                                        | Option |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| CPU                               | Texas Instruments OMAP5432 (dual-core ARM Cortex-A15 @ 1.5GHz)<br>with:<br>NEON™ SIMD Coprocessor with VFPv4 per ARM core<br>TMS320DM64 32-bit DSP,                                                                                   | C1500  |

| RAM                               | 512MB - 4GB, Dual Channel DDR3-1066 with 32-bit bus width.                                                                                                                                                                            | D      |

| Storage                           | On-board eMMC flash, 4GB to 32GB                                                                                                                                                                                                      | Ν      |

| Video<br>Processing Unit          | Dedicated IVA-HD audio/video codecs with MPEG1/2/4, H264, H263, DivX, RealVideo and more codecs support.                                                                                                                              | +      |

| Graphics<br>Acceleration<br>Units | Dual Core PowerVR SGX544 3D GPU with API support for DirectX9,<br>OpenGL-ES1.1 and 2.0, OpenVG 1.1 and OpenCL 1.1 Embedded Profile.<br>Vivante GC320 2D GPU with API support for OpenWF, DirectFB,<br>GDI/DirectDraw and Adobe Flash. | +      |

#### Table 4 I/O

| Feature                                | Specifications                                                                                     | Option |  |  |  |

|----------------------------------------|----------------------------------------------------------------------------------------------------|--------|--|--|--|

|                                        | 1x HDMI display interface (with HDMI Audio support)                                                | +      |  |  |  |

|                                        | 1x 24-bit Parallel RGB Display interface                                                           | +      |  |  |  |

| Display                                | 1x Remote Frame Buffer interface                                                                   | +      |  |  |  |

| 1 2                                    | 1x LVDS Display interface                                                                          | L      |  |  |  |

|                                        | 1x MIPI-DSI Display interface                                                                      | NOT L  |  |  |  |

| USB2.0 Host                            | 3x USB2.0 high-speed host ports, 480Mbps, implemented with SMSC USB3503 USB2.0 Hub onboard         | U4     |  |  |  |

| USB3.0 Host +<br>OTG                   | 1x USB3.0 super-speed host + OTG port, 5Gbps (backwards compatible)                                | U1     |  |  |  |

| SATA                                   | 1x SATA II interface, 3.0 Gbps, integrated controller and PHY                                      | +      |  |  |  |

| 100Mbps<br>Ethernet                    | 1x 100Base-T Ethernet MAC+PHY onboard, implemented with SMSC LAN9730 USB-to-LAN bridge.            | Е      |  |  |  |

|                                        | 1x RS-232 port - TX, RX Only, RS-232 levels. (UART4)                                               | +      |  |  |  |

| Serial Ports                           | 3x UART ports - TX, RX, CTS, RTS Only, 1.8V levels (UART1, UART2, UART5).                          | +      |  |  |  |

| (UARTs)                                | 1x UART / IrDA / CIR port - TX, RX, CTS, RTS Only, 1.8V levels.<br>(UART3)                         | +      |  |  |  |

|                                        | 1x On-board audio codec with analog stereo output, stereo input and electret<br>microphone support | А      |  |  |  |

| Audio                                  | 1x I2S compliant interface (McBSP1)                                                                | +      |  |  |  |

|                                        | 1x I2S compliant interface (McBSP3)                                                                | NOT A  |  |  |  |

|                                        | 1x Digital Microphone interface (DMIC)                                                             | NOT A  |  |  |  |

|                                        | 1x Single Lane MIPI-CSI compatible serial camera interface (MIPI-CSI-C)                            | +      |  |  |  |

| _                                      | 1x Dual Lane MIPI-CSI compatible serial camera interface (MIPI-CSI-B)                              | +      |  |  |  |

| Camera                                 | 1x Quad Lane MIPI-CSI compatible serial camera interface (MIPI-CSI-A)                              | +      |  |  |  |

|                                        | 1x Parallel camera port (up to 16 bit)                                                             | +      |  |  |  |

| RTC                                    | Real time clock, powered by external lithium battery                                               | +      |  |  |  |

| Resistive<br>Touchscreen<br>Controller | TSC2046 touchscreen controller. Supports 4-wire resistive panels                                   | Ι      |  |  |  |

| MMC/SD/SDIO                            | 2x MMC/SD/SDIO ports 1/4-bit transfer modes. (SDACRD – bootable, SDIO4)                            |        |  |  |  |

|                                        | 1x MMC/SD/SDIO port 1/4-bit transfer modes. (WLSDIO)                                               | NOT WB |  |  |  |

| WiFi and                               | Implements 802.11b/g/n wireless connectivity standard                                              |        |  |  |  |

| Bluetooth                              | Based on Marvell 88W8787. On-board connector for external antenna                                  |        |  |  |  |

| Bluetootli                             | Bluetooth 3.0 + High Speed (HS) (also compliant with Bluetooth 2.1 + EDR)                          |        |  |  |  |

| I2C                                    | 3x I2C interfaces (I2C2, I2C3, I2C4)                                                               | +      |  |  |  |

|                                        | 2x SPI interfaces (SPI1, SPI3)                                                                     | +      |  |  |  |

| SPI                                    | 1x SPI interface (SPI2)                                                                            | NOT I  |  |  |  |

|                                        | 1x SPI interface (SPI4)                                                                            | NOT WB |  |  |  |

| HDQ / 1-Wire                           | 1x HDQ/1-Wire interface                                                                            | +      |  |  |  |

| General     | Up to 106 multifunctional signals. Can be used as GPIOs (shared with other | + |

|-------------|----------------------------------------------------------------------------|---|

| Purpose I/O | functions)                                                                 | T |

| Keypad      | 1x Keypad interface with up-to 9x9 keys                                    | + |

#### Table 5 Electrical, Mechanical and Environmental Specifications

| Supply Voltage                | 3.0V to 5.5V (min 3.2V needed to boot, may be lowered after boot) |  |  |  |  |

|-------------------------------|-------------------------------------------------------------------|--|--|--|--|

| Active power                  | TBD                                                               |  |  |  |  |

| consumption                   | ענו                                                               |  |  |  |  |

| Standby/Sleep                 | TBD                                                               |  |  |  |  |

| consumption                   | IRN                                                               |  |  |  |  |

| Dimensions                    | 72 x 68 x 8 mm                                                    |  |  |  |  |

| Weight                        | 25 gram (w/o heat-plate)                                          |  |  |  |  |

| MTBF                          | > 100,000 hours                                                   |  |  |  |  |

| Operation temperature         | Commercial: 0° to 70° C                                           |  |  |  |  |

| 1 1                           | Extended: $-20^{\circ}$ to $70^{\circ}$ C                         |  |  |  |  |

| (case)                        | Industrial: -40° to 85° C                                         |  |  |  |  |

| Storage temperature           | -40° to 85° C                                                     |  |  |  |  |

| Relative humidity             | 10% to 90% (operation)                                            |  |  |  |  |

| Relative number               | 05% to 95% (storage)                                              |  |  |  |  |

| Shock                         | 50G / 20 ms                                                       |  |  |  |  |

| Vibration                     | 20G / 0 - 600 Hz                                                  |  |  |  |  |

| Connectors                    | SODIMM-204                                                        |  |  |  |  |

| Connector insertion / removal | 50 cycles                                                         |  |  |  |  |

# **3 CORE SYSTEM COMPONENTS**

### 3.1 **OMAP5432 SoC**

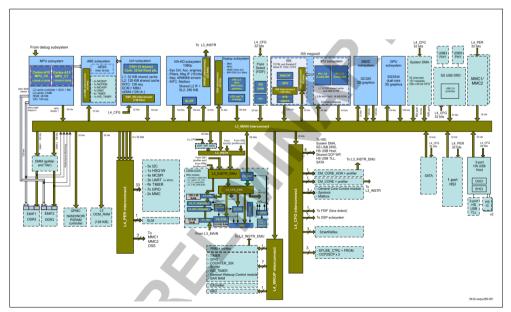

The Texas Instruments OMAP5432 SoC is a multimedia application device designed to provide bestin-class CPU performance, video, image and graphics processing for a broad range of multimediarich applications. The device includes comprehensive power management techniques required for high performance mobile products. The device is composed of the following major subsystems:

- Cortex-A15 microprocessor unit (MPU) subsystem, including two ARM Cortex-A15 cores.

- ARMv7 ISA: standard ARM instruction set plus Thumb-2, Jazelle RCT, Java accelerator, hardware virtualization support and large physical address extensions (LPAE).

- Neon SIMD coprocessor and VFPv4 per CPU.

- 32-KiB instruction and 32-KiB data L1 cache per CPU.

- Shared 2-MiB L2 cache.

- Digital signal processor (DSP) subsystem

- Image and video accelerator high-definition (IVA-HD) subsystem

- Cortex-M4 image processing unit (IPU) subsystem, including two ARM Cortex-M4 microprocessors.

- Display subsystem

- Audio back-end (ABE) subsystem

- Imaging subsystem (ISS) consisting of image processor (ISP) and still image coprocessor (SIMCOP) block.

- 3D-graphics accelerator subsystem, including POWERVR SGX544 dual-core GPU.

#### Figure 2 OMAP5432 Block Diagram

### 3.2 Multimedia System

### 3.2.1 3D and 2D Acceleration

OMAP5432 incorporates separate accelerators for 3D and 2D graphics. The dual-core PowerVR SGX544 GPU from Imagination Technologies is dedicated for 3D rendering tasks while the Vivante corporation GC230 core is dedicated for 2D graphics acceleration.

The 3D dedicated PowerVR SGX544 GPU supports the following features:

- API support for DirectX9, OpenGL-ES1.1 and 2.0, OpenVG 1.1 and OpenCL 1.1 Embedded Profile.

- Second generation universal scalable shader engines (USSE2), multithreaded engines incorporating pixel and vertex shader functionality.

- Programmable image antialiasing

- Bilinear, trilinear and anisotropic texture filtering

- RGB, ARGB, YUV422 and YUV420 surface formats

The 2D dedicated Vivante GC320 core supports the following features:

- API support for OpenWF, DirectFB, GDI/DirectDraw, Adobe Flash.

- BitBlt and StretchBlt

- DirectFB HW acceleration

- YUV-to-RGB color space rotation

- Programmable display format conversion with 14source and 7 destination formats

- 32-phase filter for image and video scaling at 1080p

- ROP2, ROP3 and ROP4 full alpha blending and transparency

- 90, 180, 270 degree rotation on every primitive

- Monochrome expansion for text rendering

#### 3.2.2 DSP subsystem

The DSP subsystem is based on a derivative of the TMS320DMC64x+ VLIW DSP core and contains the following submodules:

- TMS320DM64 32-bit fixed DSP core for audio processing and general purpose imaging and video processing, backward compatible with existing C64x video codecs.

- 32-KiB L1 4-way associative cache

- 128-KiB L2 8-way associative cache

- Dedicated DMA engine with 128 channels for video/audio data transfer between on-chip memories and DDR3 / peripherals.

- Dedicated Memory management unit (MMU) for virtual/physical address translation.

- Interrupt controller with up to 128 IRQs.

### 3.2.3 IVA-HD Subsystem

The IVA-HD subsystem is a set of video encoder/decoder hardware accelerators which supports resolutions up to 1080i/p with full performance of 60fps (or 120 fields), achievable for encode or decode (not for simultaneous encode and decode). The IVA-HD subsystem supports the following coder/decoder (codec) standards natively (all functional of these standards are accelerated without intervention of the DSP).

- H.264 BP/MP/HP encode and decode

- H.264 fast profile/RCDO encode and decode

- MPEG-4 SP/ASP encode and decode (no support for GMC)

- DivX 5.02 and higher encode/decode (no lower versions such as 3.11 and 4.x).

- H.263 P0 encode and decode, P3 decode.

- Sorenson Spark V0 and V1 decode (no encode support).

- MPEG-2 SP/MP encode/decode

- MPEG-1 encode/decode

- VC-1/WMV9/RTV SP/MP/AP encode and decode

- On2 VP6.2/VP7 decode

- RealVideo 8/9/10 decode

- AVS 1.0 encode and decode

- JPEG (also MJPEG) baseline encode and decode

- H.264 Annex G (SVC) scalable baseline profile 480p-720p30

- H.264 Annex H (MVC) up to 720p30

### 3.3 Memory

### 3.3.1 DRAM

CM-T54 is equipped with up to 4GB of onboard dual-channel DDR3 memory. Each DDR3 channel is 32-bits wide and operates at 533 MHz clock frequency (DDR3-1066).

#### NOTE: CM-T54 boards with 512MB of DRAM (D05 option) utilize only one DDR3 channel.

### 3.3.2 On-board eMMC storage

CM-T54 is available with an eMMC based onboard storage device. eMMC is the main non-volatile memory of CM-T54. It is used for boot-loader, operating system and general purpose data storage. CM-T54 (depending on board configuration) can be equipped with a 4GB, 8GB, 16GB or 32GB eMMC device.

# 4 PERIPHERAL INTERFACES

CM-T54 implements a variety of peripheral interfaces through the SODIMM-204 carrier board connector. The following notes apply to interfaces available through the SODIMM-204 interface:

- Some interfaces/signals are available only with/without certain configuration options of the CM-T54 CoM. The availability restrictions of each signal are described in the "Signals description" table for each interface.

- Many of the CM-T54 carrier board interface pins are multifunctional. Up-to 8 functions (ALT modes) are accessible through each multifunctional pin. Multifunctional pins are denoted with an asterisk (\*). For additional details, please refer to chapter 5.6.

- Only one multifunctional pin can be used for each function, configuring several multifunctional pins to implement the same function will result in unexpected system behavior.

- All of the CM-T54 digital interfaces operate at 1.8V voltage levels, unless otherwise noted.

The signals for each interface are described in the "Signal description" table for the interface in question. The following notes provide information on the "Signal description" tables:

- "Signal name" The name of each signal with regards to the discussed interface. The signal name corresponds to the relevant function in cases where the carrier board pin in question is multifunctional.

- "Pin#" The carrier board interface pin number where the discussed signal is available, multifunctional pins are denoted with an asterisk.

- "Type" Signal type, see the definition of different signal types below

- "Description" Signal description with regards to the interface in question.

- "Availability" Depending on CM-T54 Configuration options, certain carrier board interface pins are physically disconnected (floating) on-board CM-T54. The "Availability" column summarizes configuration requirements for each signal. All the listed requirements must be met (logical AND) for a signal to be "available" unless otherwise noted.

Each described signal can be one of the following types. Signal type is noted in the "Signal description" tables. Multifunctional pin direction, pull resistor and open drain functionality is software controlled. The "Type" column header for multifunctional pins refers to the recommended pin configuration with regards to the discussed signal.

- "AI" Analog Input

- "**AO**" Analog Output

- "AIO" Analog Input/Output

- "AP" Analog Power Output

- "I" Digital Input

- "O" Digital Output

- "IO" Digital Input/Output

- "OD" Open Drain Signal (not pulled up on-board CM-T54 unless otherwise noted).

- "**P**" Power

- "SPU" Software controlled pull up to 1.8V

- "SPD" Software controlled pull down to GND

- "PU18" Always pulled up to 1.8V on-board CM-T54, (typ. 5K $\Omega$ -15K $\Omega$ ).

- "**PD**" Always pulled down on-board CM-T54, (typ.  $5K\Omega$ - $15K\Omega$ ).

### 4.1 Serial ATA Interface

The CM-T54 incorporates a single SATA-II port implemented with the OMAP5432 integrated SATA controller and PHY. The interface supports the following main features:

- SATA 1.5 Gb/s and SATA 3.0 Gb/s speed.

- Support for all SATA power management features.

- Hardware-assisted Native Command Queuing (NCQ) for up to 32 entries.

- Activity LED

| Table 6 | SATA signals |

|---------|--------------|

|---------|--------------|

| Signal Name | Pin # | Туре | Description                 | Availability     |

|-------------|-------|------|-----------------------------|------------------|

| SATA_RXM    | 29    | AI   | SATA maning data main       | Always available |

| SATA_RXP    | 27    | AI   | SATA receive data pair      | Always available |

| SATA_TXM    | 23    | AO   | SATA transmit data pair     | Always available |

| SATA_TXP    | 21    | AO   | SATA transmit data pan      | Always available |

| SATA_ACTLED | 60*   | 0    | Activity led control signal | Always available |

NOTE: Pins denoted with "\*" are multifunctional. For details, please refer to section 5.6 of this document.

### 4.2 Display Interfaces

The CM-T54 display subsystem is responsible for grabbing an image from the system memory (frame buffer) and displaying that image on an LCD panel or a TV set.

The subsystem can simultaneously display different pictures using 3 independent LCD outputs (LCD1, LCD2 and LCD3) in addition a TV output. Each of the LCD outputs can be available through one of the following CM-T54 interfaces:

- Display serial interface (DSI / MIPI-DSI )

- Remote Frame Buffer interface (RFBI / MIPI DBI 2.0)

- 24 bit Parallel Display Interface (DPI)

The TV output can be available through one of the following CM-T54 interfaces:

- 24 bit Parallel Display Interface (DPI)

- High-definition multimedia interface (HDMI)

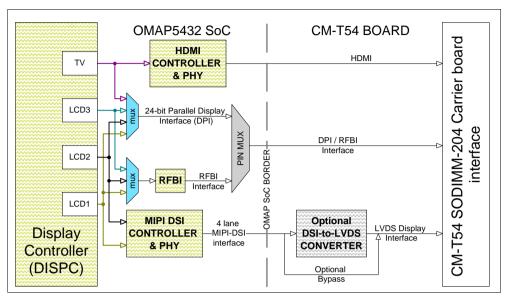

Figure 3 summarizes the display sources, relevant interfaces and architecture of the CM-T54 display subsystem.

### Figure 3 CM-T54 Display subsystem

### 4.2.1 Parallel Display Interface (DPI)

The Parallel Display interface of CM-T54 can be used to drive data from any of the display sources (LCD1, LCD2, LCD3 or TV) available with CM-T54 (see Figure 3 above). The interface is compatible with MIPI DPI protocol.

When LCD1, LCD2 or LCD3 are accessed through the parallel display interface 12, 16, 18 and 24 bit RGB modes are supported. The TV output is a 30-bit RGB interface, however only the MSB (R[9:2],G[9:2],B[9:2]) are available through the parallel RGB interface. The following standards are supported:

| Signal Name  | Pin # | Туре |           | Description |             |              |            | Availability     |

|--------------|-------|------|-----------|-------------|-------------|--------------|------------|------------------|

|              |       |      |           | -           |             |              |            |                  |

|              |       |      | 12-bit    | 16-bit      | 18-bit      | 24-bit       | 30-bit     |                  |

| DISPC_PCLK   | 98*   | 0    | Pixel clo |             |             |              |            | Always available |

| DISPC_HSYNC  | 100*  | 0    | Horizon   | tal synchro | onization   |              |            | Always available |

| DISPC_VSYNC  | 102*  | 0    | Vertical  | synchroni   | zation      |              |            | Always available |

| DISPC_DE     | 104*  | 0    | Data val  | idation/bla | ank, data e | enable       |            | Always available |

| DISPC_FID    | 66*   | 0    | The FID   | signal in   | dicates the | e field ider | ntifier of |                  |

|              |       |      | the LCD   | # output f  | ield:       |              |            | Without "I"      |

|              |       |      | 0 means   | even        |             |              |            | option           |

|              |       |      | 1 means   |             |             |              |            |                  |

| DISPC_DATA0  | 106*  | 0    | B0        | B0          | B0          | B0           | B2         | Always available |

| DISPC_DATA1  | 108*  | 0    | B1        | B1          | B1          | B1           | B3         | Always available |

| DISPC_DATA2  | 110*  | 0    | B2        | B2          | B2          | B2           | B4         | Always available |

| DISPC_DATA3  | 112*  | 0    | B3        | B3          | B3          | B3           | B5         | Always available |

| DISPC_DATA4  | 116*  | 0    | G0        | B4          | B4          | B4           | B6         | Always available |

| DISPC_DATA5  | 118*  | 0    | G1        | G0          | B5          | B5           | B7         | Always available |

| DISPC_DATA6  | 120*  | 0    | G2        | G1          | G0          | B6           | B8         | Always available |

| DISPC_DATA7  | 122*  | 0    | G3        | G2          | G1          | B7           | B9         | Always available |

| DISPC_DATA8  | 124*  | 0    | R0        | G3          | G2          | G0           | G2         | Always available |

| DISPC_DATA9  | 126*  | 0    | R1        | G4          | G3          | G1           | G3         | Always available |

| DISPC_DATA10 | 128*  | 0    | R2        | G5          | G4          | G2           | G4         | Always available |

| DISPC_DATA11 | 130*  | 0    | R3        | R0          | G5          | G3           | G5         | Always available |

| DISPC_DATA12 | 134*  | 0    |           | R1          | R0          | G4           | G6         | Always available |

| DISPC_DATA13 | 136*  | 0    |           | R2          | R1          | G5           | G7         | Always available |

| DISPC_DATA14 | 138*  | 0    |           | R3          | R2          | G6           | G8         | Always available |

| DISPC_DATA15 | 140*  | 0    |           | R4          | R3          | G7           | G9         | Always available |

| DISPC_DATA16 | 94*   | 0    |           |             | R4          | R0           | R2         | Always available |

| DISPC_DATA17 | 92*   | 0    |           |             | R5          | R1           | R3         | Always available |

Table 7

Parallel Display Interface signals

| DISPC_DATA18 | 142* | 0 |  | R2 | R4 | Always available |

|--------------|------|---|--|----|----|------------------|

| DISPC_DATA19 | 144* | 0 |  | R3 | R5 | Always available |

| DISPC_DATA20 | 146* | 0 |  | R4 | R6 | Always available |

| DISPC_DATA21 | 148* | 0 |  | R5 | R7 | Always available |

| DISPC_DATA22 | 74*  | 0 |  | R6 | R8 | Always available |

| DISPC_DATA23 | 76*  | 0 |  | R7 | R9 | Always available |

NOTE: Pins denoted with "\*" are multifunctional. For details, please refer to section 5.6 of this document.

### 4.2.2 Remote Frame buffer interface (RFBI)

The RFBI interface can be used to drive data from LCD1, LCD2 or LCD outputs of DISPC T54 (see Figure 3 above). The interface supports the following features:

- MIPI DBI protocol support.

- 8, 9, 12 and 16-bit parallel interface.

- Programmable pixel memory formats

- Programmable output formats on one or multiple cycles per pixel.

Please refer to OMAP5432 reference manual for detailed information on the RFBI interface.

| Signal Name    | Pin # | Туре | Description                                                         | Availability     |

|----------------|-------|------|---------------------------------------------------------------------|------------------|

| RFBI_RE        | 98*   | 0    | Read access signal                                                  | Always available |

| RFBI_WE        | 102*  | 0    | Write access signal                                                 | Always available |

| RFBI_A0        | 104*  | 0    | Command/Data selection signal                                       | Always available |

| RFBI_CS0       | 100*  | 0    | Chip select signal for LCD                                          | Always available |

| RFBI_TE_VSYNC0 | 94*   | Ι    | Tearing effect synchronization signal (TE or VSYNC for LCD panel 1) | Always available |

| RFBI_HSYNC0    | 92*   | Ι    | HSYNC from LCD panel                                                | Always available |

| RFBI_DATA0     | 106*  | IO   | RFBI I/O Data 0                                                     | Always available |

| RFBI_DATA1     | 108*  | IO   | RFBI I/O Data 1                                                     | Always available |

| RFBI_DATA2     | 110*  | IO   | RFBI I/O Data 2                                                     | Always available |

| RFBI_DATA3     | 112*  | IO   | RFBI I/O Data 3                                                     | Always available |

| RFBI_DATA4     | 116*  | IO   | RFBI I/O Data 4                                                     | Always available |

| RFBI_DATA5     | 118*  | IO   | RFBI I/O Data 5                                                     | Always available |

| RFBI_DATA6     | 120*  | IO   | RFBI I/O Data 6                                                     | Always available |

| RFBI_DATA7     | 122*  | IO   | RFBI I/O Data 7                                                     | Always available |

| RFBI_DATA8     | 124*  | IO   | RFBI I/O Data 8                                                     | Always available |

| RFBI_DATA9     | 126*  | IO   | RFBI I/O Data 9                                                     | Always available |

| RFBI_DATA10    | 128*  | IO   | RFBI I/O Data 10                                                    | Always available |

| RFBI_DATA11    | 130*  | IO   | RFBI I/O Data 11                                                    | Always available |

| RFBI_DATA12    | 134*  | IO   | RFBI I/O Data 12                                                    | Always available |

| RFBI_DATA13    | 136*  | IO   | RFBI I/O Data 13                                                    | Always available |

| RFBI_DATA14    | 138*  | IO   | RFBI I/O Data 14                                                    | Always available |

| RFBI_DATA15    | 140*  | IO   | RFBI I/O Data 15                                                    | Always available |

#### Table 8 Parallel Display Interface signals

NOTE: Pins denoted with "\*" are multifunctional. For details, please refer to section 5.6 of this document.

### 4.2.3 LVDS Display interface

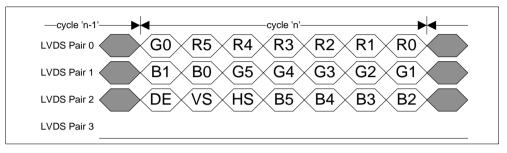

The LVDS interface can be used to transmit either LCD1 or LCD2 data of OMAP5432 DISPC (see Figure 3 above). The LVDS interface available with CM-T54 is derived by converting the MIPI-DSI data originating from OPMAP5432 into LVDS compatible data. The conversion is achieved by a

MIPI-DSI to LVDS bridge component populated onboard CM-T54. The bridge component supports the following features:

- Supports 18bpp and 24bpp DSI video packets with RGB666 and RGB888 formats.

- Max resolution up to 60fps WUXGA 1920x1200 at 18bpp and 24bpp color with reduced blanking.

- LVDS output clock range of 25MHz 154MHz.

The bridge component can send pixel data in one of the following formats (software configurable).

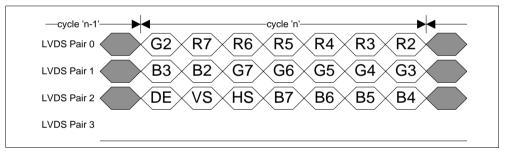

#### Figure 4 LVDS Data format A – 18bpp

#### Figure 5 LVDS Data format B – 18bpp (24bpp source to 18bpp display)

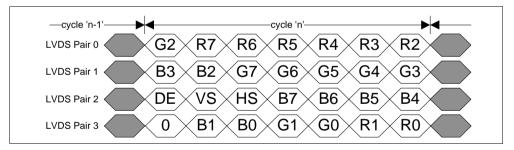

#### Figure 6 LVDS Data format C – 24bpp option 1

#### Figure 7 LVDS Data format D – 24bpp option 2

| LVDS Pair 0 GO R5 R4 R3 R2 R1 R0 |

|----------------------------------|

| LVDS Pair 1 B1 B0 G5 G4 G3 G2 G1 |

| LVDS Pair 2 DE VS HS B5 B4 B3 B2 |

| LVDS Pair 3 0 B7 B6 G7 G6 R7 R6  |

#### Table 9 LVDS Display Interfaces signals

| Signal Name | Pin # | Туре | Description              | Availability         |  |  |

|-------------|-------|------|--------------------------|----------------------|--|--|

| LVDS_CLK_N  | 35    | AO   |                          |                      |  |  |

| LVDS_CLK_P  | 33    | AO   | Differential clock pair  | Only with "L" option |  |  |

| LVDS_TX0_N  | 41    | AO   | Differential data 0 pair | Only with "L" option |  |  |

| LVDS_TX0_P  | 39    | AO   | Differential data 0 pair | Only with L option   |  |  |

| LVDS_TX1_N  | 47    | AO   | Differential data 1 main | Only with "I" ontion |  |  |

| LVDS_TX1_P  | 45    | AO   | Differential data 1 pair | Only with "L" option |  |  |

| LVDS_TX2_N  | 53    | AO   | Differential data 2 pair | Only with "I" ontion |  |  |

| LVDS_TX2_P  | 51    | AO   | Differential data 2 pair | Only with "L" option |  |  |

| LVDS_TX3_N  | 59    | AO   | Differential data 3 pair | Only with "L" option |  |  |

| LVDS_TX3_P  | 57    | AO   | Differential data 5 pair | Only with L option   |  |  |

### 4.2.4 MIPI Display Interface

The MIPI Display interface included with CM-T54 is derived from the MIPI-DSI protocol engine and the MIPI-DSI PHY integrated into the OMAP5432 SoC. The MIPI-DSI port can be used to transmit either LCD1 or LCD2 data of OMAP5432 DISPC (see Figure 3 above). The MIPI DSI interface supports the following main features:

- Up-to four data-configurable lanes in addition to one clock lane.

- Video mode and command mode support

- Bidirectional data link support for command mode (only one data lane is used in reverse direction)

- RGB16, RGB18 nonpacked, and RGB24 format support for command mode

- RGB16, RGB18 packed and nonpacked, and RGB24 format support for video mode.

- Burst for video mode

- Maximum data rate of 1256Mbps per data pair for four data lane configuration (627.75MHz)

- Data splitter for 2, 3 and 4-date lane configurations.

Please refer to OMAP5432 reference manual for detailed information on the MIPI-DSI interface.

| Signal Name     | Pin # | Туре | Description                              | Availability       |  |

|-----------------|-------|------|------------------------------------------|--------------------|--|

| DSIPORTA_LANE0Y | 35    | IO   | 1 <sup>st</sup> lane (serial data/clock) | Without "I" antion |  |

| DSIPORTA_LANE0X | 33    | IO   | 1 Talle (serial data/clock)              | Without "L" option |  |

| DSIPORTA_LANE1Y | 41    | IO   | 2 <sup>nd</sup> lane (serial data/clock) | Without "I" antion |  |

| DSIPORTA_LANE1X | 39    | IO   | 2 Talle (serial data/clock)              | Without "L" option |  |

| DSIPORTA_LANE2Y | 47    | IO   | 3 <sup>rd</sup> lane (serial data/clock) | Without "L" option |  |

| DSIPORTA_LANE2X | 45    | IO   | 5 Talle (Serial data/clock)              | without L option   |  |

| DSIPORTA_LANE3Y | 53    | IO   | 4 <sup>th</sup> lane (serial data/clock) | Without "L" option |  |

| DSIPORTA_LANE3X | 51    | IO   | 4 Talle (Serial data/clock)              | without L option   |  |

| DSIPORTA_LANE4Y | 59    | IO   | $5^{\text{th}}$ lane (serial data only)  | Without "L" option |  |

| DSIPORTA_LANE4X | 57    | IO   | 5 Tane (serial data only)                | without L option   |  |

| DSIPORTA_TE0    | 75*   | Ι    | DSI1 tearing effect (TE) input 0         | Always available   |  |

| Table 10 | MIPI Dis | play | Interface | signals |

|----------|----------|------|-----------|---------|

|----------|----------|------|-----------|---------|

NOTE: Pins denoted with "\*" are multifunctional. For details, please refer to section 5.6 of this document.

### 4.2.5 HDMI port

Please refer to chapter 4.5 of this document for detailed description of HDMI port.

### 4.3 Camera Interfaces

CM-T54 Camera interfaces are derived from the OMAP5432 imaging subsystem (ISS). The OMAP5432 imaging subsystem deals with the processing of the pixel data coming from an external image sensor, data from memory (image format encoding and decoding can be done to and from memory) or from the IVA-HD subsystem. The ISS external image sensor interfaces include three serial camera interfaces and a single parallel camera interface.

### 4.3.1 Parallel Camera Interface

The parallel camera interface available with CM-T54 supports the following features:

- 8bit, 12bit or 16bit input data bus.

- Interface Clock frequency of up to 148.5MPix/s

- Configurable pixel clock polarity

- BT656 and SYNC mode (HS, VS, FIELD, WEN)

Please refer to OMAP5432 reference manual for detailed information on the parallel camera interface.

| Pin # | Туре                                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Availability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 93*   | 0                                                                                                                                                                                              | Flash strobe control signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 81*   | 0                                                                                                                                                                                              | Machanical shutter control signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 0                                                                                                                                                                                              | Weenamear shutter control signar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 99*   | IO                                                                                                                                                                                             | Camera global reset release signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | IO                                                                                                                                                                                             | Pixel clock field signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 95*   | Ι                                                                                                                                                                                              | Pixel clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 97*   | Ι                                                                                                                                                                                              | Write enable signal input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 113*  | Ι                                                                                                                                                                                              | Vertical frame synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 115*  | Ι                                                                                                                                                                                              | Horizontal frame synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 101*  | Ι                                                                                                                                                                                              | Input data 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 103*  | Ι                                                                                                                                                                                              | Input data 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 89*   | Ι                                                                                                                                                                                              | Input data 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 91*   | Ι                                                                                                                                                                                              | Input data 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 77*   | Ι                                                                                                                                                                                              | Input data 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 79*   | Ι                                                                                                                                                                                              | Input data 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 83*   | Ι                                                                                                                                                                                              | Input data 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 85*   | Ι                                                                                                                                                                                              | Input data 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 107*  | Ι                                                                                                                                                                                              | Input data 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 109*  | Ι                                                                                                                                                                                              | Input data 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 121*  | Ι                                                                                                                                                                                              | Input data 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

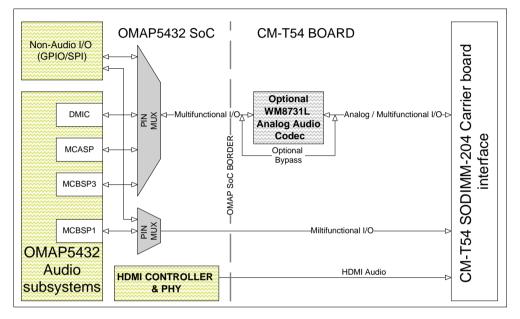

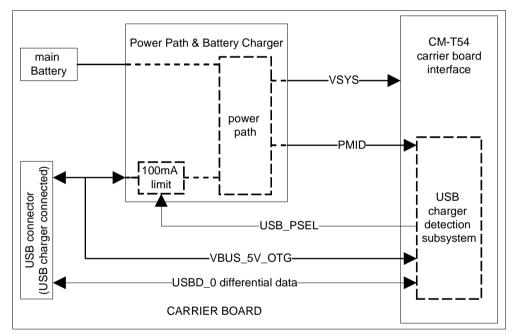

| 119*  | Ι                                                                                                                                                                                              | Input data 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Always available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |