**Reference Guide**

## © 2018 Compulab Ltd.

All Rights Reserved. No part of this document may be photocopied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means whether, electronic, mechanical, or otherwise without the prior written permission of Compulab Ltd.

No warranty of accuracy is given concerning the contents of the information contained in this publication. To the extent permitted by law, no liability (including liability to any person by reason of negligence) will be accepted by Compulab Ltd., its subsidiaries or employees for any direct or indirect loss or damage caused by omissions from or inaccuracies in this document.

Compulab Ltd. reserves the right to change details in this publication without notice.

Product and company names herein may be the trademarks of their respective owners.

Compulab Ltd. P.O. Box 687 Yokneam Illit 20692 ISRAEL Tel: +972 (4) 8290100 https://www.compulab.com Fax: +972 (4) 8325251

## **Table of Contents**

| 1 | IN                                  | TRODUCTION                                          | 6   |

|---|-------------------------------------|-----------------------------------------------------|-----|

|   | 1.1                                 | About This Document                                 | 6   |

|   | 1.2                                 | UCM-iMX8 Part Number Legend                         | 6   |

|   | 1.3                                 | Related Documents                                   | 6   |

| 2 | 0                                   | VERVIEW                                             | 7   |

| 4 |                                     |                                                     |     |

|   | 2.1                                 | Highlights                                          |     |

|   | 2.2                                 | Block Diagram<br>UCM-iMX8 Features                  |     |

|   | 2.3                                 | UCM-IMX8 Features                                   | 8   |

| 3 | C                                   | ORE SYSTEM COMPONENTS                               |     |

|   | 3.1                                 | iMX8M SoC                                           | .10 |

|   | 3.2                                 | Memory                                              | .10 |

|   | 3.                                  | 2.1 DRAM                                            | .10 |

|   | 3.                                  | 2.2 Bootloader and General Purpose Storage          | .10 |

| 4 | Pl                                  | ERIPHERAL INTERFACES                                | .11 |

|   | 4.1                                 | HDMI                                                | .12 |

|   | 4.2                                 | MIPI-DSI Interface                                  | .12 |

|   | 4.3                                 | Camera Serial Interface                             | .13 |

|   | 4.4                                 | Ethernet                                            | .14 |

|   | 4.                                  | 4.1 RGMII                                           | .14 |

|   | 4.5                                 | Wireless Interface                                  | .14 |

|   | 4.6                                 | PCI-Express                                         | .15 |

|   | 4.7                                 | Sony/Philips Digital Interface (SPDIF)              | .16 |

|   | 4.8                                 |                                                     |     |

|   | 4.9                                 | Digital Audio (SAI)                                 |     |

|   | 4.10                                | USB3.0 ports                                        |     |

|   | 4.11                                | MMC / SD /SDIO                                      |     |

|   | 4.12                                | UART                                                |     |

|   | 4.13                                | I2C                                                 |     |

|   | 4.14                                | ECSPI                                               |     |

|   | 4.15                                | JTAG                                                |     |

|   | 4.16                                | QSPI                                                |     |

|   | <ul><li>4.17</li><li>4.18</li></ul> | NAND<br>PWM                                         |     |

|   | 4.10                                | GPIO                                                |     |

|   | 4.17                                | 0110                                                | .25 |

| 5 | S                                   | YSTEM LOGIC                                         | .27 |

|   | 5.1                                 | Power Supply                                        |     |

|   | 5.2                                 | System and Miscellaneous Signals                    |     |

|   |                                     | 2.1 External regulator control and power management |     |

|   | 5.3                                 | Reset                                               | .27 |

|        | 5.4                           | Boot Sequence                                                                                                                                                     |

|--------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 5.5                           | Signal Multiplexing Characteristics                                                                                                                               |

|        | 5.6                           | RTC                                                                                                                                                               |

|        | 5.7                           | LED                                                                                                                                                               |

| 6      | С                             | ARRIER BOARD INTERFACE                                                                                                                                            |

|        | 6.1                           | Connectors Pinout                                                                                                                                                 |

|        | 6.2                           | Mating Connectors                                                                                                                                                 |

|        | 6.3                           | Mechanical Drawings                                                                                                                                               |

|        | 6.4                           | Heat Spreader and Cooling Solutions                                                                                                                               |

|        |                               |                                                                                                                                                                   |

| 7      |                               | PERATIONAL CHARACTERISTICS                                                                                                                                        |

| 7      |                               |                                                                                                                                                                   |

| 7      | 0                             | PERATIONAL CHARACTERISTICS                                                                                                                                        |

| 7      | <b>0</b><br>7.1               | PERATIONAL CHARACTERISTICS                                                                                                                                        |

| 7<br>8 | <b>0</b><br>7.1<br>7.2<br>7.3 | PERATIONAL CHARACTERISTICS                                                                                                                                        |

|        | <b>0</b><br>7.1<br>7.2<br>7.3 | <b>PERATIONAL CHARACTERISTICS</b> 37         Absolute Maximum Ratings       37         Recommended Operating Conditions       37         ESD Performance       37 |

#### Table 1 Revision Notes

| Date     | Description   |  |  |  |  |

|----------|---------------|--|--|--|--|

| Nov 2018 | First release |  |  |  |  |

Please check for a newer revision of this manual at the CompuLab website https://www.compulab.com. Compare the revision notes of the updated manual from the website with those of the printed or electronic version you have.

#### **INTRODUCTION** 1

#### 1.1 **About This Document**

This document is part of a set of reference documents providing information necessary to operate and program CompuLab UCM-iMX8 Computer-on-Module.

#### 1.2 UCM-iMX8 Part Number Legend

Please refer to the CompuLab website 'Ordering information' section to decode the UCM-iMX8 part number: https://www.compulab.com/products/computer-on-modules/ucm-imx8-nxp-i-mx-8m-som-system-on-module-computer/#ordering.

#### 1.3 **Related Documents**

Table 2

For additional information, refer to the documents listed in Table 2.

|  | Related Documents |  |

|--|-------------------|--|

|  | Document          |  |

Related Documents

| Document                     | Location                                                                                                                                                                                                                                        |  |  |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| UCM-iMX8 Developer Resources | https://www.compulab.com/products/computer-on-<br>modules/ucm-imx8-nxp-i-mx-8m-som-system-on-module-<br>computer/#devres                                                                                                                        |  |  |

| iMX8M Reference Manual       | https://www.nxp.com/products/processors-and-<br>microcontrollers/arm-based-processors-and-mcus/i.mx-<br>applications-processors/i.mx-8-processors/i.mx-8m-<br>family-armcortex-a53-cortex-m4-audio-voice-<br>video:i.MX8M?tab=Documentation_Tab |  |  |

| iMX8M Datasheet              | https://www.nxp.com/products/processors-and-<br>microcontrollers/arm-based-processors-and-mcus/i.mx-<br>applications-processors/i.mx-8-processors/i.mx-8m-<br>family-armcortex-a53-cortex-m4-audio-voice-<br>video:i.MX8M?tab=Documentation_Tab |  |  |

## 2 OVERVIEW

## 2.1 Highlights

- NXP i.MX8M ARM Cortex-A53 MPCore 1.5GHz

- Real-time ARM Cortex-M4 co-processor

- Up to 4GB LPDDR4 and 64GB eMMC

- HDMI 2.0a, MIPI-DSI, up to 4096 x 2160

- Gbit Ethernet, certified WiFi 802.11ac, BT 4.1

- 2x PCIe, 2x USB3.0, 4x UART, 95x GPIO

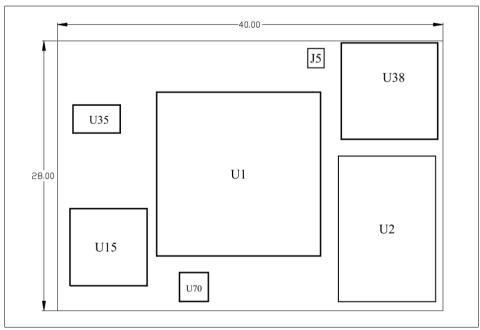

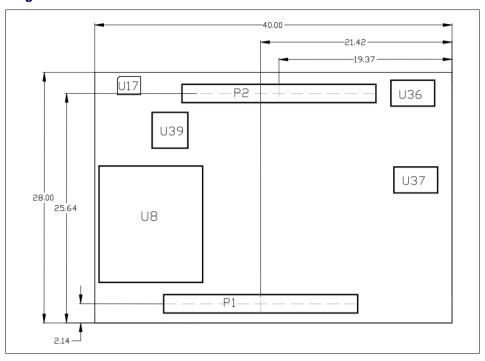

- Miniature size: 28 x 40 x 5 mm

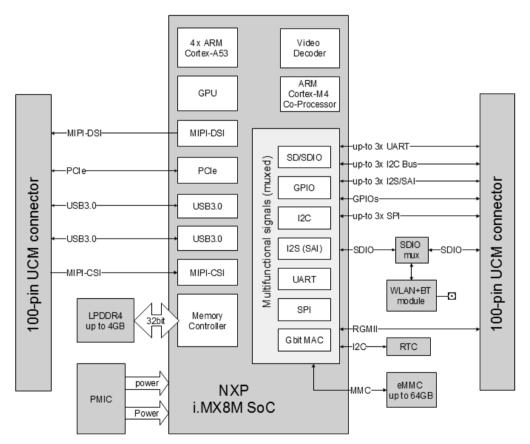

## 2.2 Block Diagram

### Figure 1 UCM-iMX8 Block Diagram

## 2.3 UCM-iMX8 Features

The "Option" column specifies the CoM/SoM configuration option required to have the particular feature. When a CoM/SoM configuration option is prefixed by "NOT", the particular feature is only available when the option is not used. A feature is only available when a CoM/SoM configuration complies with all options denoted in the "Option" column. "+" means that the feature is always available.

| Table 3 | Features and Configuration options |  |

|---------|------------------------------------|--|

|---------|------------------------------------|--|

| Feature                                  | Feature Description                                                                                        |               |  |  |  |  |  |  |  |

|------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------|--|--|--|--|--|--|--|

| CPU Core and Graphics                    |                                                                                                            |               |  |  |  |  |  |  |  |

| CPU                                      | CPU NXP i.MX8M Quad, quad-core ARM Cortex-A53, 1.5GHz<br>NXP i.MX8M Dual, dual-core ARM Cortex-A53, 1.5GHz |               |  |  |  |  |  |  |  |

|                                          | NXP i.MX8M Dual, dual-core ARM Cortex-A53, 1.5GHz     C1500D       Memory and Storage                      |               |  |  |  |  |  |  |  |

| RAM                                      | 1GB – 4GB, LPDDR4                                                                                          | D             |  |  |  |  |  |  |  |

| Storage                                  | eMMC flash, 4GB - 64GB                                                                                     | N             |  |  |  |  |  |  |  |

|                                          | Display and Camera                                                                                         |               |  |  |  |  |  |  |  |

|                                          | HDMI 2.0a, up-to 4096 x 2160 @60Hz                                                                         | +             |  |  |  |  |  |  |  |

| Display                                  | MIPI-DSI 4 lanes up to FHD (1920 x 1080) @60Hz                                                             | +             |  |  |  |  |  |  |  |

| Camera                                   | MIPI-CSI, 4 lanes                                                                                          | +             |  |  |  |  |  |  |  |

|                                          | Network                                                                                                    |               |  |  |  |  |  |  |  |

| Ethernet                                 | 1x 10/100/1000Mbps Ethernet port (RGMII)                                                                   | +             |  |  |  |  |  |  |  |

| WiFi                                     | 802.11ac WiFi interface, Broadcom BCM43353 chipset<br>*precludes MMC/SD/SDIO port                          | WB            |  |  |  |  |  |  |  |

| Bluetooth Bluetooth 4.2 BLE              |                                                                                                            |               |  |  |  |  |  |  |  |

|                                          | Audio                                                                                                      | •             |  |  |  |  |  |  |  |

| Distal Andis                             | Up-to 3x I2S / SAI                                                                                         | +             |  |  |  |  |  |  |  |

| Digital Audio                            | S/PDIF input/output                                                                                        | +             |  |  |  |  |  |  |  |

|                                          | I/O                                                                                                        |               |  |  |  |  |  |  |  |

| PCI Express                              | 2x PCIe x1 Gen. 2.1                                                                                        | +             |  |  |  |  |  |  |  |

| USB                                      | 2x USB3.0 dual-role ports                                                                                  | +             |  |  |  |  |  |  |  |

| Serial Ports                             | 1x UART debug port - TX, RX Only, levels (UART3)                                                           | +             |  |  |  |  |  |  |  |

| (UARTs)                                  | Up to 2x UART ports, up to 4 Mbps                                                                          | +             |  |  |  |  |  |  |  |

| (UAK1S)                                  | 1x UART port - TX, RX, CTS, RTS                                                                            | <del>WB</del> |  |  |  |  |  |  |  |

| MMC/SD/SDIO                              | Up to 1x MMC/SD/SDIO                                                                                       | +             |  |  |  |  |  |  |  |

|                                          | *mutually exclusive with WiFi module                                                                       | 1             |  |  |  |  |  |  |  |

| SPI Up to 3x SPI                         |                                                                                                            |               |  |  |  |  |  |  |  |

| I2C                                      | Up to 3x I2C                                                                                               | + +           |  |  |  |  |  |  |  |

| PWM Up to 4x general purpose PWM signals |                                                                                                            |               |  |  |  |  |  |  |  |

| GPIO                                     | Up to 95x GPIO (multifunctional signals shared with other functions)                                       | +             |  |  |  |  |  |  |  |

|                                          | System Logic                                                                                               |               |  |  |  |  |  |  |  |

| -                                        | RTC Real-time clock, powered by external battery                                                           |               |  |  |  |  |  |  |  |

| JTAG JTAG debug interface                |                                                                                                            |               |  |  |  |  |  |  |  |

|                              | Electrical Specifications     | Electrical Specifications |  |  |

|------------------------------|-------------------------------|---------------------------|--|--|

| Supply Voltage               | 3.6V to 4.4V                  | 3.6V to 4.4V              |  |  |

| Digital I/O voltage          | 3.3V                          |                           |  |  |

|                              | Mechanical Specifications     |                           |  |  |

| Dimensions                   | 28 x 40 x 5 mm                |                           |  |  |

| Weight                       | 8 gram                        |                           |  |  |

| Connectors                   | 2 x 100 pin, 0.4mm pitch      |                           |  |  |

|                              | Environmental and Reliability |                           |  |  |

| MTTF                         | > 200,000 hours               |                           |  |  |

|                              | Commercial: 0° to 70° C       |                           |  |  |

| Operation temperature (case) | Extended: -20° to 70° C       |                           |  |  |

|                              | Industrial: -40° to 85° C     |                           |  |  |

| Storage temperature          | -40° to 85° C                 |                           |  |  |

| Deletive humidity            | 10% to 90% (operation)        |                           |  |  |

| Relative humidity            | 05% to 95% (storage)          |                           |  |  |

| Shock                        | 50G / 20 ms                   |                           |  |  |

| Vibration                    | 20G / 0 - 600 Hz              |                           |  |  |

### Table 4 Electrical, Mechanical and Environmental Specifications

## **3 CORE SYSTEM COMPONENTS**

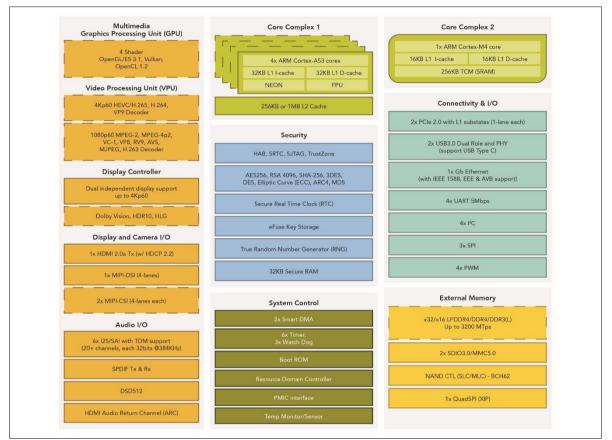

## 3.1 iMX8M SoC

The i.MX 8M family of processors features advanced implementation of a quad ARM® Cortex®-A53 core, which operates at speeds of up to 1.5 GHz. A general purpose Cortex®-M4 core processor is for low-power processing.

#### Figure 2 i.MX8M Block Diagram

## 3.2 Memory

### 3.2.1 DRAM

UCM-iMX8 is equipped with up to 4GB of onboard LPDDR4 memory. The LPDDR4 channel is 32-bits wide and operates at 1600 MHz clock frequency (LPDDR4-3200).

### 3.2.2 Bootloader and General Purpose Storage

The UCM-iMX8 uses on-board non-volatile memory (eMMC) storage as its bootloader host. The remaining eMMC space is designed to store the operating system (kernel & root filesystem) and general purpose (user) data.

## 4 PERIPHERAL INTERFACES

UCM-iMX8 implements a variety of peripheral interfaces through  $2 \ge 100$ -pin (0.4mm pitch) carrier board connectors. The following notes apply to interfaces available through the  $2 \ge 100$ -pin interfaces:

- Some interfaces/signals are available only with/without certain configuration options of the UCM-iMX8 SoM. The availability restrictions of each signal are described in the "Signals description" table for each interface.

- Some of the UCM-iMX8 carrier board interface pins are multifunctional. Up to 4 functions (ALT modes) are accessible through each multifunctional pin. Multifunctional pins are denoted with an asterisk (\*). For additional details, please refer to chapter 5.5.

- All of the UCM-iMX8 digital interfaces operate at 3.3V voltage levels unless otherwise noted.

The signals for each interface are described in the "Signal description" table for the interface in question. The following notes provide information on the "Signal description" tables:

- **"Signal name"** The name of each signal with regards to the discussed interface. The signal name corresponds to the relevant function in cases where the carrier board pin in question is multifunctional.

- "Connector#" The carrier board connector number (P1/P2) where the discussed signal is available.

- "Pin#" The carrier board interface pin number where the discussed signal is available, multifunctional pins are denoted with an asterisk.

- **"Type"** Signal type, see the definition of different signal types below

- "Description" Signal description with regards to the interface in question.

- "Availability" Depending on UCM-iMX8 Configuration options, certain carrier board interface pins are physically disconnected (floating) on-board UCM-iMX8. The "Availability" column summarizes configuration requirements for each signal. All the listed requirements must be met (logical AND) for a signal to be "available" unless otherwise noted.

Each described signal can be one of the following types. Signal type is noted in the "Signal description" tables. Multifunctional pin direction, pull resistor, and open drain functionality is software controlled. The "Type" column header for multifunctional pins refers to the recommended pin configuration with regards to the discussed signal.

- "AI" Analog Input

- "AO" Analog Output

- "AIO" Analog Input/Output

- "AP" Analog Power Output

- "I" Digital Input

- "O" Digital Output

- "IO" Digital Input/Output

- "**P**" Power

- "PD" Always pulled down onboard UCM-IMX8, followed by pull value.

- "PU" Always pulled up onboard UCM-IMX8, followed by pull value.

- "LVDS" Low-voltage differential signaling.

## 4.1 **HDMI**

UCM-iMX8 HDMI 2.0 interface is derived from the i.MX8M HD Display Transmitter Controller IP. For more detailed information, please refer to the i.MX8M TRM chapter 13: HD Display Transmitter Controller (HDMI TX).

The controller supports the following protocols:

- HDMI 1.4 Specification.

- HDMI 2.0a Specification.

- High-bandwidth Digital Content Protection system, Mapping HDCP to HDMI, Revision 2.2.

- High-bandwidth Digital Content Protection system, Mapping HDCP to HDMI, Revision 1.4.

- CEA-861-F.

The table below summarizes the HDMI interface signals

| Signal Name  | Connector<br># | Pin<br># | Туре | Description                         | Availability     |

|--------------|----------------|----------|------|-------------------------------------|------------------|

| HDMI_AUXN    | P1             | 61       | IO   | HEAC -                              | Always available |

| HDMI_AUXP    | P1             | 59       | IO   | HEAC +                              | Always available |

| HDMI_CEC     | P1             | 62       | Ι    | Consumer Electronics Control        | Always available |

| HDMI_CLKN_CM | P1             | 52       | 0    | TMDS Clock-                         | Always available |

| HDMI_CLKP_CM | P1             | 50       | 0    | TMDS Clock+                         | Always available |

| HDMI_DDC_SCL | P1             | 58       | 0    | Data Display Channel clock          | Always available |

| HDMI_DDC_SDA | P1             | 56       | Ю    | Data Display Channel data<br>signal | Always available |

| HDMI_HPD     | P1             | 60       | Ι    | Hot Plug Detect                     | Always available |

| HDMI_TXN0_CM | P1             | 49       | 0    | TMDS Data0-                         | Always available |

| HDMI_TXN1_CM | P1             | 55       | 0    | TMDS Data1-                         | Always available |

| HDMI_TXN2_CM | P1             | 45       | 0    | TMDS Data2-                         | Always available |

| HDMI_TXP0_CM | P1             | 51       | 0    | TMDS Data0+                         | Always available |

| HDMI_TXP1_CM | P1             | 53       | 0    | TMDS Data1+                         | Always available |

| HDMI_TXP2_CM | P1             | 47       | 0    | TMDS Data2+                         | Always available |

Table 5HDMI Interface Signals

## 4.2 MIPI-DSI Interface

The UCM-iMX8 MIPI-DSI interface is derived from the four-lane MIPI display interface available on the iMX8M SoC. The following main features are supported:

- Scalable data lane support, 1 to 4 Data Lanes.

- Supports MIPI Standard for D-PHY.

- Implements all three DSI Layers (Pixel to Byte packing, Low Level Protocol, Lane Management)

- Maximum resolution ranges up to FHD (1920 x 1080 @ 60 Hz).

- MIPI Alliance Specification for Display Serial Interface Version 1.1 compliant

The table below summarizes the MIPI-DSI interface signals

| Signal<br>Name | Connector<br># | Pin<br># | Туре | Description                                    | Availability     |  |  |  |

|----------------|----------------|----------|------|------------------------------------------------|------------------|--|--|--|

| DSI_CKN        | P2             | 21       | 0    | Negative part of MIPI-DSI clock diff-pair      | Always available |  |  |  |

| DSI_CKP        | P2             | 23       | 0    | Positive part of MIPI-DSI clock diff-<br>pair  | Always available |  |  |  |

| DSI_DN0        | P2             | 1        | 0    | Negative part of MIPI-DSI data diff-<br>pair 0 | Always available |  |  |  |

| DSI_DN1        | P2             | 15       | 0    | Negative part of MIPI-DSI data diff-<br>pair 2 | Always available |  |  |  |

#### Table 6 MIPI-DSI Interface Signals

| Signal<br>Name | Connector<br># | Pin<br># | Туре | Description                                    | Availability     |

|----------------|----------------|----------|------|------------------------------------------------|------------------|

| DSI_DN2        | P2             | 5 0      |      | Negative part of MIPI-DSI data diff-<br>pair 2 | Always available |

| DSI_DN3        | P2             | 11       | 0    | Negative part of MIPI-DSI data diff-<br>pair 2 | Always available |

| DSI_DP0        | P2             | 3        | 0    | Positive part of MIPI-DSI data diff-<br>pair 0 | Always available |

| DSI_DP1        | P2             | 17       | 0    | Positive part of MIPI-DSI data diff-<br>pair 1 | Always available |

| DSI_DP2        | P2             | 7        | 0    | Positive part of MIPI-DSI data diff-<br>pair 2 | Always available |

| DSI_DP3        | P2             | 13       | 0    | Positive part of MIPI-DSI data diff-<br>pair 3 | Always available |

## 4.3 Camera Serial Interface

UCM-iMX8 MIPI-CSI interface is derived from the four-lane MIPI CSI1 host controller (MIPI\_CSI1) integrated into the iMX8M SoC. The CSI1 host controller is a digital core that implements all protocol functions defined in the MIPI CSI-1 specification, providing an interface between UCM-iMX8 and a MIPI CSI-1 compliant camera sensor. The following main features are supported:

- Up-to four data lanes and one clock lane.

- Maximum bit rate of 1.5 Gbps.

- Compliant with MIPI D-PHY standard specification V1.1 and Samsung D-PHY.

- Compliant to MIPI CSI2 Standard Specification V1.01r06.

- Supports primary and secondary image format:

- YUV420, YUV420 (Legacy), YUV420 (CSPS), YUV422 of 8-bits and 10-bits.

- RGB565, RGB666, RGB888

- RAW6, RAW7, RAW8, RAW10, RAW12, RAW14

- Compressed format: 10-6-10, 10-7-10, 10-8-10, 14-10-14

Please refer to the iMX8M Reference manual for additional details. The table below summarizes the MIPI-CSI interface signals

| Signal Name | Connector<br># | Pin<br># | Туре | Description                                    | Availability     |

|-------------|----------------|----------|------|------------------------------------------------|------------------|

| CSI_P1_CKN  | P2             | 2        | 0    | Negative part of MIPI-<br>CSI clock diff-pair  | Always available |

| CSI_P1_CKP  | P2             | 4        | 0    | Positive part of MIPI-CSI<br>clock diff-pair   | Always available |

| CSI_P1_DN0  | P2             | 6        | Ι    | Negative part of MIPI-<br>CSI data diff-pair 0 | Always available |

| CSI_P1_DN1  | P2             | 31       | Ι    | Negative part of MIPI-<br>CSI data diff-pair 1 | Always available |

| CSI_P1_DN2  | P2             | 25       | Ι    | Negative part of MIPI-<br>CSI data diff-pair 2 | Always available |

| CSI_P1_DN3  | P2             | 35       | Ι    | Negative part of MIPI-<br>CSI data diff-pair 3 | Always available |

| CSI_P1_DP0  | P2             | 8        | Ι    | Positive part of MIPI-CSI<br>data diff-pair 0  | Always available |

| CSI_P1_DP1  | P2             | 33       | Ι    | Positive part of MIPI-CSI data diff-pair 1     | Always available |

| CSI_P1_DP2  | P2             | 27       | Ι    | Positive part of MIPI-CSI data diff-pair 2     | Always available |

| CSI_P1_DP3  | P2             | 37       | Ι    | Positive part of MIPI-CSI data diff-pair 3     | Always available |

Table 7 MIPI-CSI Interface Signals

## 4.4 Ethernet

iMX8M incorporates an internal MAC controller that can be used with an external PHY to implement 10/100/1000 Mbps Ethernet interface.

### 4.4.1 **RGMII**

The iMX8M Ethernet MAC RGMII and MDIO lines are routed directly to the carrier board interface. Please refer to the iMX8M Reference manual for additional details.

The table below summarizes the Ethernet RGMII interface signals

| Signal Name | Connector<br># | Pin<br># | Туре | Description                                                                                                                                  | Availability        |

|-------------|----------------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| ENET_MDC    | P2             | 76*      | 0    | Provides a timing reference to the<br>PHY for data transfers on the MDIO<br>signal                                                           | Always<br>available |

| ENET_MDC    | P1             | 100*     | 0    | Provides a timing reference to the<br>PHY for data transfers on the MDIO<br>signal                                                           | Always<br>available |

| ENET_MDIO   | P2             | 88*      | Ю    | Transfers control information between<br>the external PHY and the MAC. Data<br>is synchronous to MDC. This signal is<br>an input after reset | Always<br>available |

| ENET_MDIO   | P1             | 96*      | Ю    | Transfers control information between<br>the external PHY and the MAC. Data<br>is synchronous to MDC. This signal is<br>an input after reset | Always<br>available |

| ENET_RD0    | P2             | 86*      | Ι    | Ethernet input data from the PHY                                                                                                             | Always<br>available |

| ENET_RD1    | P2             | 83*      | Ι    | Ethernet input data from the PHY                                                                                                             | Always<br>available |

| ENET_RD2    | P2             | 84*      | Ι    | Ethernet input data from the PHY                                                                                                             | Always<br>available |

| ENET_RD3    | P2             | 85*      | Ι    | Ethernet input data from the PHY                                                                                                             | Always<br>available |

| ENET_RX_CTL | P2             | 79*      | I    | Contains RX_EN on the rising edge of<br>RGMII_RXC, and RX_EN XOR<br>RX_ER on the falling edge of<br>RGMII_RXC (RGMII mode).                  | Always<br>available |

| ENET_RXC    | P2             | 80*      | Ι    | Timing reference for RX_DATA[3:0]<br>and RX_CTL in RGMII MODE                                                                                | Always<br>available |

| ENET_TD0    | P2             | 75*      | 0    | Ethernet output data to PHY                                                                                                                  | Always<br>available |

| ENET_TD1    | P2             | 78*      | 0    | Ethernet output data to PHY                                                                                                                  | Always<br>available |

| ENET_TD2    | P2             | 77*      | 0    | Ethernet output data to PHY                                                                                                                  | Always<br>available |

| ENET_TD3    | P2             | 73*      | 0    | Ethernet output data to PHY                                                                                                                  | Always<br>available |

| ENET_TXC    | P2             | 81*      | 0    | Timing reference for TX_DATA[3:0]<br>and TX_CTL in RGMII MODE                                                                                | Always<br>available |

| ENET_TX_CTL | P2             | 74*      | О    | Contains TX_EN on the rising edge of<br>RGMII_TXC, and TX_EN XOR<br>TX_ER on the falling edge of<br>RGMII_TXC (RGMII mode).                  | Always<br>available |

Table 8 Ethernet RGMII Interface Signals

NOTE: Pins denoted with "\*" are multifunctional. For additional details please refer to chapter 5 of this document

## 4.5 Wireless Interface

UCM-iMX8 optional 802.11a/b/g/n/ac WLAN and Bluetooth 4.2/EDR functions are implemented with the Cypress BCM43353 chipset. i.MX8M SoC is interfaced with the WLAN Cypress subsystem over i.MX8M SDIO interface, while UART4 is dedicated to Bluetooth functionality.

UCM-iMX8 is equipped with a MHF4 high-frequency connector allowing easy integration with an external WLAN/BT antenna.

#### Table 9J5 MHF4 connector data

| Manufacturer | Mfg. P/N       | Mating Connector      |

|--------------|----------------|-----------------------|

| Hirose       | W.FL2-R-MT(60) | Hirose W.FL2-LP-062HF |

NOTE: UCM-iMX8 WiFi 802.11 a/b/g/n and Bluetooth functionality is available only with the 'WB' ordering option.

### 4.6 PCI-Express

iMX8M SoC is equipped with two single lane PCI Express port (PCIe) Gen 2.1 ports. UCM-iMX8 enables access to the iMX8M PCI-Express ports (PCIe 1 & 2) through the carrier board interface. PCIe #1 has a built in PCIe reference clock and does not require an external clock source, while PCIe #2 requires an external PCIe clock to be supplied in order to utilize the interface. The PCI Express ports support the following main features:

- Single lane compliant with PCI Express base specification Gen 2.1 (5.0Gbps).

- Dual mode operation to function as root complex or endpoint.

- Integrated PHY interface.

- Supports spread spectrum clocking in transmitter and receiver.

Please refer to the iMX8M Reference manual for additional details. The tables below summarize the PCI Express interface signals

| Signal Name    | Connector<br># | Pin<br># | Туре | Description                                                           | Availability        |

|----------------|----------------|----------|------|-----------------------------------------------------------------------|---------------------|

| PCIE1_CLKREQ_B | P1             | 87*      | Ι    | PCIe clock request signal                                             | Always<br>available |

| PCIE1_CLKREQ_B | P1             | 84*      | Ι    | PCIe clock request signal                                             | Always<br>available |

| PCIE1_REF_CLKN | P2             | 44       | 0    | 100 MHz negative-side reference clock<br>differential output for PCIe | Always<br>available |

| PCIE1_REF_CLKP | P2             | 42       | 0    | 100 MHz positive-side reference clock<br>differential output for PCIe | Always<br>available |

| PCIE1_RXN_N    | P2             | 30       | Ι    | PCI Express receive data negative                                     | Always<br>available |

| PCIE1_RXN_P    | P2             | 32       | Ι    | PCI Express receive data positive                                     | Always<br>available |

| PCIE1_TXN_N    | P2             | 36       | 0    | PCI Express transmit data negative                                    | Always<br>available |

| PCIE1_TXN_P    | P2             | 38       | 0    | PCI Express transmit data positive                                    | Always<br>available |

#### Table 10 PCIE 1 Interface Signals

#### Table 11 PCIE 2 Interface Signals

| Signal Name    | Connector<br># | Pin<br># | Туре | Description                                                                                                                           | Availability        |

|----------------|----------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| PCIE2_CLKREQ_B | P1             | 89*      | Ι    | PCIe clock request signal                                                                                                             | Always<br>available |

| PCIE2_CLKREQ_B | P1             | 86*      | Ι    | PCIe clock request signal                                                                                                             | Always<br>available |

| PCIE2_REF_CLKN | P2             | 26       | Ι    | 100 MHz negative-side reference clock<br>differential output for PCIe. Must be pulled<br>low through 49.9Ω resistor on carrier board. | Always<br>available |

| PCIE2_REF_CLKP | P2             | 24       | Ι    | 100 MHz positive-side reference clock<br>differential output for PCIe. Must be pulled<br>low through 49.9Ω resistor on carrier board. | Always<br>available |

| PCIE2_RXN_N    | P2             | 12       | Ι    | PCI Express receive data negative                                                                                                     | Always<br>available |

| Signal Name | Connector<br># | Pin<br># | Туре | Description                        | Availability        |

|-------------|----------------|----------|------|------------------------------------|---------------------|

| PCIE2_RXN_P | P2             | 14       | Ι    | PCI Express receive data positive  | Always<br>available |

| PCIE2_TXN_N | P2             | 18       | 0    | PCI Express transmit data negative | Always<br>available |

| PCIE2_TXN_P | P2             | 20       | 0    | PCI Express transmit data positive | Always<br>available |

NOTE: Pins denoted with "\*" are multifunctional. For additional details please refer to chapter 5 of this document

## 4.7 Sony/Philips Digital Interface (SPDIF)

UCM-iMX8 provides one SPDIF transmitter with one output and one SPDIF receiver with one input.

Please refer to the iMX8M Reference manual for additional details. The table below summarizes the SPDIF interface signals

| Table 12 S | <b>SPDIF Interface</b> | Signals |

|------------|------------------------|---------|

|------------|------------------------|---------|

| Signal Name   | Connector<br># | Pin # | Туре | Description                   | Availability     |

|---------------|----------------|-------|------|-------------------------------|------------------|

| SPDIF_EXT_CLK | P1             | 77*   | Ι    | External clock signal         | Always available |

| SPDIF_RX      | P1             | 79*   | Ι    | SPDIF input data line signal  | Always available |

| SPDIF_TX      | P1             | 81*   | 0    | SPDIF output data line signal | Always available |

NOTE: Pins denoted with "\*" are multifunctional. For additional details please refer to chapter 5 of this document

## 4.8 Digital Audio (SAI)

UCM-iMX8 enables access to 3 of the iMX8M integrated synchronous audio interface (SAI) modules. The SAI module provides a synchronous audio interface (SAI) that supports full duplex serial interfaces with frame synchronization, such as I2S, AC97, TDM, and codec/DSP interfaces. The following main features are supported:

- One transmitter with independent bit clock and frame sync supporting 1 data line. One receiver with independent bit clock and frame sync supporting 1 data line.

- Maximum Frame Size of 32 words.

- Word size of between 8-bits and 32-bits. Separate word size configuration for the first word and remaining words in the frame.

- Asynchronous 32 × 32-bit FIFO for each transmit and receive channel

Please refer to the iMX8M Reference manual for additional details. The tables below summarize the SAI interface signals

| Signal Name | Connector<br># | Pin<br># | Туре | Description                                                                                           | Availability        |

|-------------|----------------|----------|------|-------------------------------------------------------------------------------------------------------|---------------------|

| SAI2_MCLK   | P1             | 30*      | Ю    | Audio master clock. An input when<br>generated externally and an output when<br>generated internally. | Always<br>available |

| SAI2_RXD    | P1             | 28*      | Ι    | Receive data, sampled synchronously by the bit clock                                                  | Always<br>available |

| SAI2_RXC    | P1             | 32*      | Ι    | Receive bit clock. An input when generated<br>externally and an output when generated<br>internally.  | Always<br>available |

#### Table 13 SAI 2 Interface Signals

| Signal Name | Connector<br># | Pin<br># | Туре | Description                                                                                                                                      | Availability        |

|-------------|----------------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| SAI2_RXFS   | P1             | 34*      | Ι    | Receive frame sync. An input sampled by bit<br>clock when generated externally. A bit clock<br>synchronous output when generated<br>internally.  | Always<br>available |

| SAI2_TXD    | P1             | 26*      | 0    | Transmit data signal synchronous to bit<br>clock. Tristated whenever not transmitting a<br>word                                                  | Always<br>available |

| SAI2_TXC    | P1             | 36*      | 0    | Transmit bit clock. An input when generated externally and an output when generated internally.                                                  | Always<br>available |

| SAI2_TXFS   | P1             | 38*      | 0    | Transmit frame sync. An input sampled by<br>bit clock when generated externally. A bit<br>clock synchronous output when generated<br>internally. | Always<br>available |

### Table 14 SAI 3 Interface Signals

| Signal Name | Connector<br># | Pin<br># | Туре | Description                                                                                                                                      | Availability        |

|-------------|----------------|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| SAI3_MCLK   | P1             | 17*      | Ю    | Audio master clock. An input when<br>generated externally and an output when<br>generated internally.                                            | Always<br>available |

| SAI3_RXD    | P1             | 19*      | Ι    | Receive data, sampled synchronously by the bit clock                                                                                             | Always<br>available |

| SAI3_RXC    | P1             | 21*      | Ι    | Receive bit clock. An input when generated<br>externally and an output when generated<br>internally.                                             | Always<br>available |

| SAI3_RXFS   | P1             | 25*      | Ι    | Receive frame sync. An input sampled by bit<br>clock when generated externally. A bit clock<br>synchronous output when generated<br>internally.  | Always<br>available |

| SAI3_TXD    | P1             | 13*      | 0    | Transmit data signal synchronous to bit<br>clock. Tristated whenever not transmitting a<br>word                                                  | Always<br>available |

| SAI3_TXC    | P1             | 15*      | 0    | Transmit bit clock. An input when generated externally and an output when generated internally.                                                  | Always<br>available |

| SAI3_TXFS   | P1             | 23*      | 0    | Transmit frame sync. An input sampled by<br>bit clock when generated externally. A bit<br>clock synchronous output when generated<br>internally. | Always<br>available |

## Table 15 SAI 5 Interface Signals

| Signal Name  | Connector<br># | Pin<br># | Туре | Description                                                                                           | Availability        |

|--------------|----------------|----------|------|-------------------------------------------------------------------------------------------------------|---------------------|

| SAI5_MCLK    | P1             | 41*      | Ю    | Audio master clock. An input<br>when generated externally and an<br>output when generated internally. | Always<br>available |

| SAI5_MCLK    | P1             | 30*      | Ю    | Audio master clock. An input<br>when generated externally and an<br>output when generated internally. | Always<br>available |

| SAI5_MCLK    | P1             | 17*      | Ю    | Audio master clock. An input<br>when generated externally and an<br>output when generated internally. | Always<br>available |

| SAI5_RX_BCLK | P1             | 21*      | Ι    | Receive bit clock. An input when<br>generated externally and an output<br>when generated internally.  | Always<br>available |

| SAI5_RXD0    | P1             | 35*      | Ι    | Receive data, sampled<br>synchronously by the bit clock                                               | Always<br>available |

| SAI5_RXD0    | P1             | 19*      | Ι    | Receive data, sampled<br>synchronously by the bit clock                                               | Always<br>available |

| SAI5_RXD1    | P1             | 33*      | Ι    | Receive data, sampled<br>synchronously by the bit clock                                               | Always<br>available |

| SAI5_RXD1    | P1             | 23*      | Ι    | Receive data, sampled<br>synchronously by the bit clock                                               | Always<br>available |

| SAI5_RXD2    | P1             | 37*      | Ι    | Receive data, sampled<br>synchronously by the bit clock                                               | Always<br>available |

| SAI5_RXD2    | P1             | 15*      | Ι    | Receive data, sampled synchronously by the bit clock                                                  | Always<br>available |

| Signal Name     | Connector<br># | Pin<br># | Туре | Description                                                                                                                                         | Availability        |

|-----------------|----------------|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| SAI5_RXD3       | P1             | 29*      | Ι    | Receive data, sampled<br>synchronously by the bit clock                                                                                             | Always<br>available |

| SAI5_RXD3       | P1             | 13*      | Ι    | Receive data, sampled<br>synchronously by the bit clock                                                                                             | Always<br>available |

| SAI5_RXC        | P1             | 31*      | Ι    | Receive bit clock. An input when<br>generated externally and an output<br>when generated internally.                                                | Always<br>available |

| SAI5_RXFS       | P1             | 39*      | Ι    | Receive frame sync. An input<br>sampled by bit clock when<br>generated externally. A bit clock<br>synchronous output when<br>generated internally.  | Always<br>available |

| SAI5_RX_SYNC    | P1             | 25*      | Ι    | Receive frame sync. An input<br>sampled by bit clock when<br>generated externally. A bit clock<br>synchronous output when<br>generated internally.  | Always<br>available |

| SAI5_TX_BCLK    | P1             | 37*      | 0    | Transmit bit clock. An input<br>when generated externally and an<br>output when generated internally.                                               | Always<br>available |

| SAI5_TX_BCLK    | P1             | 32*      | 0    | Transmit bit clock. An input<br>when generated externally and an<br>output when generated internally.                                               | Always<br>available |

| SAI5_TX_DATA[0] | P1             | 29*      | 0    | Transmit data signal synchronous<br>to bit clock. Tristated whenever<br>not transmitting a word                                                     | Always<br>available |

| SAI5_TX_DATA[0] | P1             | 28*      | 0    | Transmit data signal synchronous<br>to bit clock. Tristated whenever<br>not transmitting a word                                                     | Always<br>available |

| SAI5_TX_DATA[1] | P1             | 38*      | 0    | Transmit data signal synchronous<br>to bit clock. Tristated whenever<br>not transmitting a word                                                     | Always<br>available |

| SAI5_TX_DATA[2] | P1             | 36*      | 0    | Transmit data signal synchronous<br>to bit clock. Tristated whenever<br>not transmitting a word                                                     | Always<br>available |

| SAI5_TX_DATA[3] | P1             | 26*      | 0    | Transmit data signal synchronous<br>to bit clock. Tristated whenever<br>not transmitting a word                                                     | Always<br>available |

| SAI5_TX_SYNC    | P1             | 34*      | 0    | Transmit frame sync. An input<br>sampled by bit clock when<br>generated externally. A bit clock<br>synchronous output when<br>generated internally. | Always<br>available |

| SAI5_TX_SYNC    | P1             | 33*      | 0    | Transmit frame sync. An input<br>sampled by bit clock when<br>generated externally. A bit clock<br>synchronous output when<br>generated internally. | Always<br>available |

NOTE: Pins denoted with "\*" are multifunctional. For additional details please refer to chapter 5 of this document

## 4.9 USB3.0 ports

iMX8M SoC is equipped with two USB controllers and PHYs that support USB 3.0 and USB 2.0. Each USB instance contains USB 3.0 core, which can operate in both 3.0 and 2.0 mode. One port supports dual-role functionality, while the second port is configured permanently for host mode. USB ports support the following main features:

- SuperSpeed, Hi Speed and Full Speed support.

- USB3 U1/U2/U3 Support.

- 32 endpoints per slot.

- Separate Power Domains for Host and Peripheral Device logic.

- Full Power Management capabilities (U1, U2 and U3) with LFPS support for

SuperSpeed.

Please refer to the iMX8M Reference manual for additional details.

The tables below summarize the USB3.0 interface signals

#### Table 16 USB3.0 1 Interface Signals

| Signal Name   | Connector<br># | Pin # | Туре | Description                   | Availability     |

|---------------|----------------|-------|------|-------------------------------|------------------|

| USB1_DN       | P1             | 14    | IO   | USB2.0 negative data          | Always available |

| USB1_DP       | P1             | 12    | IO   | USB2.0 positive data          | Always available |

| USB1_ID       | P1             | 22    | Ι    | USB1 OTG ID signal            | Always available |

| USB1_RX_N     | P1             | 18    | Ι    | USB3.0 receive negative lane  | Always available |

| USB1_RX_P     | P1             | 16    | Ι    | USB3.0 receive positive lane  | Always available |

| USB1_TX_N     | P1             | 8     | 0    | USB3.0 transmit negative lane | Always available |

| USB1_TX_P     | P1             | 6     | 0    | USB3.0 transmit positive lane | Always available |

| USB1_VBUS_DET | P1             | 24    | Ι    | USB1 VBUS detect              | Always available |

#### Table 17 USB3.0 2 Interface Signals

| Signal Name   | Connector<br># | Pin # | Туре | Description                   | Availability     |

|---------------|----------------|-------|------|-------------------------------|------------------|

| USB2_DN       | P1             | 5     | IO   | USB2.0 negative data          | Always available |

| USB2_DP       | P1             | 3     | IO   | USB2.0 positive data          | Always available |

| USB2_RX_N     | P1             | 9     | Ι    | USB3.0 receive negative lane  | Always available |

| USB2_RX_P     | P1             | 7     | Ι    | USB3.0 receive positive lane  | Always available |

| USB2_TX_N     | P1             | 2     | 0    | USB3.0 transmit negative lane | Always available |

| USB2_TX_P     | P1             | 4     | 0    | USB3.0 transmit positive lane | Always available |

| USB2_VBUS_DET | P1             | 1     | Ι    | USB2 VBUS detect              | Always available |

## 4.10 MMC / SD /SDIO

UCM-iMX8 features one MMC/SD/SDIO port which is mutually functionally exclusive with the on-board WiFi module. The i.MX8M SDIO interface is routed by on-board multiplexing circuitry either to the on-board WiFi module or to the carrier-board interface connector. SDIO multiplexing is controlled by GPIO\_IO13. If "WB" option is not populated, the SDIO interface is always available.

The port is derived from the iMX8M on-chip MMC/SD/SDIO controller (uSDHC). uSDHC IP supports the following main features:

- Fully compliant with MMC command/response sets and physical layer as defined in the multimedia card system specification, v5.0/v4.4/v4.41/v4.4/v4.3/v4.2.

- Fully compliant with SD command/response sets and physical layer as defined in the SD memory card specifications, v3.0 including high-capacity SDXC cards up to 2 TB.

- 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR104 mode (104 MB/s max).

- 1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 200 MHz in both SDR and DDR modes, including HS400 (8-bit transfer mode is only available on uSDHC port 1).

- Dedicated card detection, write protection and Reset signals.

Please refer to the iMX8M Reference manual for additional details.

The table below summarizes the MMC/SD/SDIO interface signals

| ······································ |                |          |      |                            |                                  |  |  |  |  |

|----------------------------------------|----------------|----------|------|----------------------------|----------------------------------|--|--|--|--|

| Signal Name                            | Connector<br># | Pin<br># | Туре | Description                | Availability                     |  |  |  |  |

| SD2_nCD                                | P2             | 92*      | Ι    | Card detection pin         | Always<br>available              |  |  |  |  |

| EXT_SD2_CLK                            | P2             | 96*      | 0    | Clock for MMC/SD/SDIO card | GPIO_IO13<br>is low or not<br>WB |  |  |  |  |

#### Table 18 MMC/SD/SDIO Interface Signals

| Signal Name   | Connector<br># | Pin<br># | Туре | Description                                                                                                                  | Availability                     |

|---------------|----------------|----------|------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| EXT_SD2_CMD   | P2             | 100*     | Ю    | CMD line connect to card                                                                                                     | GPIO_IO13<br>is low or not<br>WB |

| EXT_SD2_DATA0 | P2             | 97*      | Ю    | DATA0 line in all modes. Also used to detect busy state                                                                      | GPIO_IO13<br>is low or not<br>WB |

| EXT_SD2_DATA1 | P2             | 99*      | Ю    | DATA1 line in 4/8-bit mode. Also used to detect interrupt in 1/4- bit mode                                                   | GPIO_IO13<br>is low or not<br>WB |

| EXT_SD2_DATA2 | P2             | 94*      | Ю    | DATA2 line or Read Wait in 4-bit mode.<br>Read Wait in 1-bit mode                                                            | GPIO_IO13<br>is low or not<br>WB |

| EXT_SD2_DATA3 | P2             | 98*      | Ю    | DATA3 line in 4/8-bit mode or configured as<br>card detection pin. May be configured as<br>card detection pin in 1-bit mode. | GPIO_IO13<br>is low or not<br>WB |

| SD2_nRST      | P2             | 51*      | 0    | Card hardware reset signal, active LOW                                                                                       | Always<br>available              |

| SD2_WP        | P2             | 49*      | Ι    | Card write protect detection                                                                                                 | Always<br>available              |

NOTE: Pins denoted with "\*" are multifunctional. For additional details please refer to chapter 5 of this document

## 4.11 UART

UCM-iMX8 enables access to up-to four iMX8M universal asynchronous receiver/transmitter (UART) modules based on the UARTv2 IP. The iMX8M UARTv2 supports the following features:

- High-speed TIA/EIA-232-F compatible.

- 7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none).

- Programmable baud rates up to 4 Mbps.

- 32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud.

- Serial IR interface low-speed, IrDA-compatible (up to 115.2 Kbit/s).

- Hardware flow control support for a request to send and clear to send signals.

- RS-485 driver direction control.

- DCE/DTE capability.

- RX\_DATA input and TX\_DATA output can be inverted respectively in RS-232/RS-485 mode.

- Various asynchronous wake mechanisms with the capability to wake the processor from STOP mode through an on-chip interrupt.

# NOTE: The UART4 is used for the on-board Bluetooth module. Using UART4 interface signals available through the carrier board interface precludes on-board Bluetooth operation.

Please refer to the iMX8M Reference manual for additional details.

The tables below summarize the UART interface signals

#### Table 19 UART 1 Interface Signals

| Signal Name | Connector<br># | Pin # | Туре | Description                 | Availability     |

|-------------|----------------|-------|------|-----------------------------|------------------|

| UART1_CTS_B | P1             | 76*   | 0    | UART-1 clear to send        | Always available |

| UART1_RTS_B | P1             | 74*   | Ι    | UART-1 request to send      | Always available |

| UART1_RXD   | P1             | 70*   | Ι    | UART-1 serial data receive  | Always available |

| UART1_TXD   | P1             | 72*   | 0    | UART-1 serial data transmit | Always available |

| Signal Name | Connector<br># | Pin # | Туре | Description                 | Availability     |

|-------------|----------------|-------|------|-----------------------------|------------------|

| UART2_CTS_B | P1             | 84*   | 0    | UART-2 clear to send        | Always available |

| UART2_RTS_B | P1             | 86*   | Ι    | UART-2 request to send      | Always available |

| UART2_RXD   | P1             | 80*   | Ι    | UART-2 serial data receive  | Always available |

| UART2_TXD   | P1             | 82*   | 0    | UART-2 serial data transmit | Always available |

#### Table 20 UART 2 Interface Signals

#### Table 21 UART 3 Interface Signals

| Signal Name  | Connector<br># | Pin # | Туре | Description                    | Availability     |

|--------------|----------------|-------|------|--------------------------------|------------------|

| DBG_UART_RXD | P1             | 76*   | Ι    | UART-3 serial data receive     | Always available |

| DBG_UART_TXD | P1             | 74*   | 0    | UART-3 serial data<br>transmit | Always available |

#### Table 22 UART 4 Interface Signals

| Signal Name | Connector<br># | Pin #                        | Туре                       | Description                    | Availability                                |

|-------------|----------------|------------------------------|----------------------------|--------------------------------|---------------------------------------------|

| UART4 RXD   | P1             | 84*                          | Ι                          | UART-4 serial data receive     | Always available,<br>precludes<br>Bluetooth |

|             | P2             | 93* I UART-4 seri<br>receive | UART-4 serial data receive | Only w/o "WB"<br>option        |                                             |

| UART4_TXD   | P1             | 86*                          | 0                          | UART-4 serial data<br>transmit | Always available,<br>precludes<br>Bluetooth |

|             |                | 95*                          | 0                          | UART-4 serial data transmit    | Only w/o "WB"<br>option                     |

| UART4_CTS_B | P2             | 89*                          | 0                          | UART-4 clear to send           | Only w/o "WB"<br>option                     |

| UART4_RTS_B | P2             | 91*                          | Ι                          | UART-4 request to send         | Only w/o "WB"<br>option                     |

# NOTE: Pins denoted with "\*" are multifunctional. For additional details please refer to chapter 5 of this document

## 4.12 I2C

UCM-iMX8 is equipped with up-to three I2C bus interfaces. The following general features are supported by all I2C bus interfaces:

- Compliant with Philips I2C specification version 2.1

- Supports standard mode (up to 100K bits/s) and fast mode (up to 400K bits/s)

- Multimaster operation

- Master or Slave operation mode.

Please refer to the iMX8M Reference manual for additional details.

The tables below summarize the I2C interface signals

#### Table 23 I2C 1 Interface Signals

| Signal Name | Connector<br># | Pin # | Туре | Description           | Availability     |

|-------------|----------------|-------|------|-----------------------|------------------|

| I2C1_SCL    | P1             | 100*  | 0    | I2C serial clock line | Always available |

| I2C1_SDA    | P1             | 96*   | IO   | I2C serial data line  | Always available |

#### Table 24I2C 3 Interface Signals

| Signal Name | Connector<br># | Pin # | Туре | Description           | Availability     |

|-------------|----------------|-------|------|-----------------------|------------------|

| I2C3_SCL    | P1             | 94*   | 0    | I2C serial clock line | Always available |

| I2C3_SDA    | P1             | 91*   | IO   | I2C serial data line  | Always available |

| Signal Name | Connector<br># | Pin # | Туре | Description           | Availability     |

|-------------|----------------|-------|------|-----------------------|------------------|

| I2C4_SCL    | P1             | 87*   | 0    | I2C serial clock line | Always available |

| I2C4_SDA    | P1             | 89*   | IO   | Always available      | Always available |

#### Table 25 I2C 4 Interface Signals

NOTE: Pins denoted with "\*" are multifunctional. For additional details please refer to chapter 5 of this document

## 4.13 ECSPI

Up-to three SPI interfaces are accessible through the UCM-iMX8 carrier board interface. The SPI interfaces are derived from iMX8M integrated synchronous serial interface (eCSPI). Each instance of the eCSPI port can operate as either a master or as an SPI slave. The following features are supported:

- Data rate up to 52 Mbit/s.

- Full-duplex synchronous serial interface.

- Master/Slave configurable.

- Up-to four chip select signals to support multiple peripherals.

- Transfer continuation function allows unlimited length data transfers.

- 32-bit wide by 64-entry FIFO for both transmit and receive data.

- Polarity and phase of the Chip Select (SS) and SPI Clock (SCLK) are configurable.

- Direct Memory Access (DMA) support.

Please refer to the iMX8M Reference manual for additional details.

The tables below summarize the ECSPI interface signals

#### Table 26 ECSPI 1 Interface Signals

| Signal Name | Connector<br># | Pin # | Туре | Description                            | Availability     |

|-------------|----------------|-------|------|----------------------------------------|------------------|

| ECSPI1_MISO | P1             | 44*   | Ι    | SPI-1 Master data in; slave data out   | Always available |

| ECSPI1_MOSI | P1             | 42*   | 0    | SPI-1 Master data out; slave data in   | Always available |

| ECSPI1_SCLK | P1             | 48*   | 0    | SPI-1 Master clock out; slave clock in | Always available |

| ECSPI1_SS0  | P1             | 46*   | 0    | SPI-1 Chip select 0                    | Always available |

#### Table 27 ECSPI 2 Interface Signals

| Signal Name | Connector<br># | Pin # | Туре | Description                            | Availability            |

|-------------|----------------|-------|------|----------------------------------------|-------------------------|

| ECSPI2_MISO | P2             | 89*   | Ι    | SPI-2 Master data in; slave data out   | Only w/o "WB"<br>option |

| ECSPI2_MOSI | P2             | 95*   | 0    | SPI-2 Master data out; slave data in   | Only w/o "WB"<br>option |

| ECSPI2_SCLK | P2             | 93*   | 0    | SPI-2 Master clock out; slave clock in | Only w/o "WB"<br>option |

| ECSPI2_SS0  | P2             | 91*   | 0    | SPI-2 Chip select 0                    | Only w/o "WB"<br>option |

#### Table 28 ECSPI 3 Interface Signals

| Signal Name | Connector<br># | Pin # | Туре | Description                            | Availability     |

|-------------|----------------|-------|------|----------------------------------------|------------------|

| ECSPI3_MISO | P1             | 80*   | Ι    | SPI-3 Master data in; slave data out   | Always available |

| ECSPI3_MOSI | P1             | 72*   | 0    | SPI-3 Master data out; slave data in   | Always available |

| ECSPI3_SCLK | P1             | 70*   | 0    | SPI-3 Master clock out; slave clock in | Always available |

| ECSPI3_SS0  | P1             | 82*   | 0    | SPI-3 Chip select 0                    | Always available |

NOTE: Pins denoted with "\*" are multifunctional. For additional details please refer to chapter 5 of this document

## 4.14 JTAG

UCM-iMX8 enables access to the iMX8M JTAG port through the carrier board interface.

Please refer to the iMX8M Reference manual for additional details.

The table below summarizes the JTAG interface signals

| Signal Name | Connector<br># | Pin # | Туре | Description      | Availability     |

|-------------|----------------|-------|------|------------------|------------------|

| JTAG_MOD    | P1             | 75    | Ι    | JTAG MODE        | Always available |

| JTAG_nTRST  | P1             | 63    | Ι    | Test Reset       | Always available |

| JTAG_TCK    | P1             | 73    | Ι    | Test Clock       | Always available |

| JTAG_TDI    | P1             | 71    | Ι    | Test Data In     | Always available |

| JTAG_TDO    | P1             | 67    | 0    | Test Data Out    | Always available |

| JTAG_TMS    | P1             | 65    | Ι    | Test Mode Select | Always available |

#### Table 29 JTAG Interface Signals

## 4.15 **QSPI**

UCM-iMX8 is equipped with two instances of the Quad SPI interface. The interface is implemented with the iMX8M integrated QSPI controller. The following features are supported by the QSPI controller:

- Flexible sequence engine to support various flash vendor devices.

- Single pad, dual pad or quad pad mode of operation.

- Single data rate/double data rate mode of operation.

- Parallel Flash mode.

- Direct Memory Access (DMA) support.

- Memory mapped read access to connected flash devices.

- Multi-master access with priority and flexible and configurable buffer for each master.

Please refer to the iMX8M Reference manual for additional details.

The tables below summarize the QSPI interface signals

#### Table 30 QSPI A Interface Signals

| Signal Name  | Connector<br># | Pin<br># | Туре | Description                                    | Availability     |

|--------------|----------------|----------|------|------------------------------------------------|------------------|

| QSPI_A_DATA0 | P2             | 61*      | IO   | Data IO 0                                      | Always available |

| QSPI_A_DATA1 | P2             | 56*      | IO   | Data IO 1                                      | Always available |

| QSPI_A_DATA2 | P2             | 43*      | IO   | Data IO 2                                      | Always available |

| QSPI_A_DATA3 | P2             | 58*      | IO   | Data IO 3                                      | Always available |

| QSPI_A_DQS   | P2             | 67*      | 0    | Data strobe signal to serial flash device<br>A | Always available |

| QSPI_A_SCLK  | P2             | 55*      | 0    | Serial clock                                   | Always available |

| QSPI_A_SS0_B | P2             | 65*      | 0    | Chip select 0                                  | Always available |

| QSPI_A_SS1_B | P2             | 53*      | 0    | Chip select 1                                  | Always available |

#### Table 31 QSPI B Interface Signals

| Signal Name  | Connector<br># | Pin<br># | Туре | Description | Availability     |

|--------------|----------------|----------|------|-------------|------------------|

| QSPI_B_DATA0 | P2             | 48*      | IO   | Data IO 0   | Always available |

| QSPI_B_DATA1 | P2             | 59*      | IO   | Data IO 1   | Always available |

| QSPI_B_DATA2 | P2             | 63*      | IO   | Data IO 2   | Always available |

| QSPI_B_DATA3 | P2             | 69*      | IO   | Data IO 3   | Always available |

| Signal Name  | Connector<br># | Pin<br># | Туре | Description                                    | Availability     |

|--------------|----------------|----------|------|------------------------------------------------|------------------|

| QSPI_B_DQS   | P2             | 50*      | 0    | Data strobe signal to serial flash device<br>B | Always available |

| QSPI_B_SCLK  | P2             | 62*      | 0    | Serial clock                                   | Always available |

| QSPI_B_SS0_B | P2             | 41*      | 0    | Chip select 0                                  | Always available |

| QSPI_B_SS1_B | P2             | 60*      | 0    | Chip select 1                                  | Always available |

NOTE: Pins denoted with "\*" are multifunctional. For additional details please refer to chapter 5 of this document

## 4.16 NAND

8-bit NAND-Flash is implemented with the iMX8M GPMI controller.

The table below summarizes the NAND interface signals

| Signal Name | Connector<br># | Pin # | Туре | Description               | Availability     |

|-------------|----------------|-------|------|---------------------------|------------------|

| NAND_ALE    | P2             | 55*   | 0    | NAND address latch enable | Always available |

| NAND_nCE0   | P2             | 65*   | 0    | NAND chip enable 0        | Always available |

| NAND_nCE1   | P2             | 53*   | 0    | NAND chip enable 1        | Always available |

| NAND_nCE2   | P2             | 41*   | 0    | NAND chip enable 2        | Always available |

| NAND_nCE3   | P2             | 60*   | 0    | NAND chip enable 3        | Always available |

| NAND_CLE    | P2             | 62*   | 0    | NAND command latch enable | Always available |

| NAND_DATA0  | P2             | 61*   | IO   | NAND data IO 0            | Always available |

| NAND_DATA1  | P2             | 56*   | IO   | NAND data IO 1            | Always available |

| NAND_DATA2  | P2             | 43*   | IO   | NAND data IO 2            | Always available |

| NAND_DATA3  | P2             | 58*   | IO   | NAND data IO 3            | Always available |

| NAND_DATA4  | P2             | 48*   | IO   | NAND data IO 4            | Always available |

| NAND_DATA5  | P2             | 59*   | IO   | NAND data IO 5            | Always available |

| NAND_DATA6  | P2             | 63*   | IO   | NAND data IO 6            | Always available |

| NAND_DATA7  | P2             | 69*   | IO   | NAND data IO 7            | Always available |

| NAND_DQS    | P2             | 67*   | Ι    | NAND DQS strobe           | Always available |

| NAND_nRE    | P2             | 50*   | 0    | NAND read enable          | Always available |

| NAND_nREADY | P2             | 52*   | Ι    | NAND ready ready/busy     | Always available |

| NAND_nWE    | P2             | 47*   | 0    | NAND write enable         | Always available |

| NAND_nWP    | P2             | 45*   | 0    | NAND write protect        | Always available |

#### Table 32 NAND Interface Signals

NOTE: Pins denoted with "\*" are multifunctional. For additional details please refer to chapter 5 of this document

## 4.17 **PWM**

Up to four independent PWM output signals are available at the UCM-iMX8 carrier board interface. The following key features are supported:

- 16-bit up-counter with clock source selection

- 4 x 16 FIFO to minimize interrupt overhead

- 12-bit prescaler for division of clock

- Sound and melody generation

- Active high or active low configured output

- Interrupts at compare and rollover

Please refer to the iMX8M Reference manual for additional details.

The table below summarizes the PWM interface signals

| Signal Name | Connector<br># | Pin # | Туре | Description           | Availability     |

|-------------|----------------|-------|------|-----------------------|------------------|

| PWM1 OUT    | P1             | 77*   | 0    | PWM functional output | Always available |